RD74LVC16373B

Overview

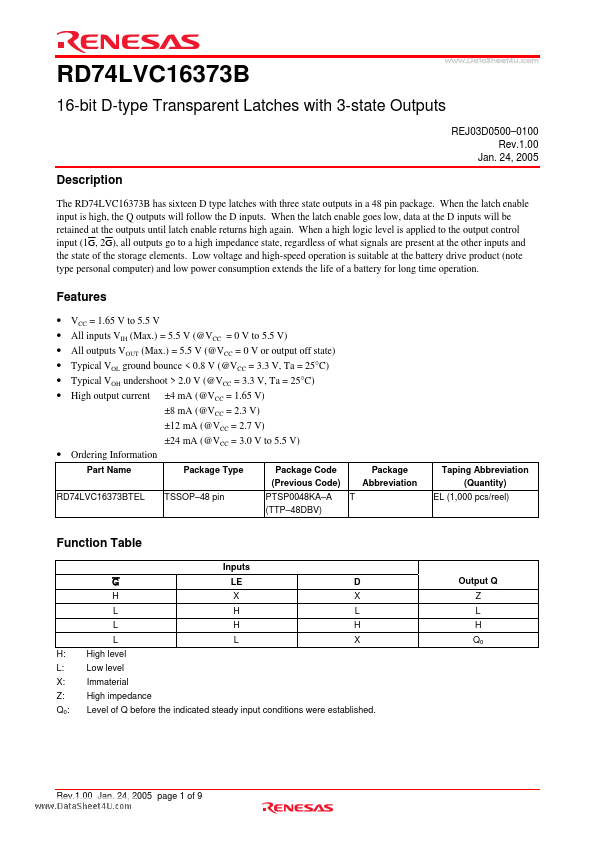

The RD74LVC16373B has sixteen D type latches with three state outputs in a 48 pin package. When the latch enable input is high, the Q outputs will follow the D inputs.

- VCC = 1.65 V to 5.5 V All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V) All outputs VOUT (Max.) = 5.5 V (@VCC = 0 V or output off state) Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C) Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C) High output current ±4 mA (@VCC = 1.65 V) ±8 mA (@VCC = 2.3 V) ±12 mA (@VCC = 2.7 V) ±24 mA (@VCC = 3.0 V to 5.5 V)