| Part | M54HC699 |

|---|---|

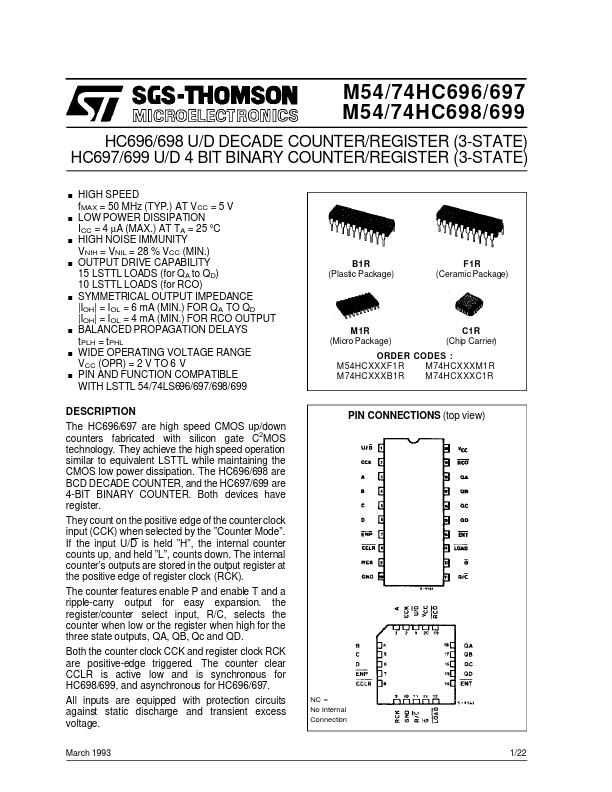

| Description | HC697/699 U/D 4 BIT BINARY COUNTER/REGISTER 3-STATE HC696/698 U/D DECADE COUNTER/REGISTER 3-STATE |

| Manufacturer | STMicroelectronics |

| Size | 429.86 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CBT16211 | NXP Semiconductors | OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| 74125 | Fairchild Semiconductor | Quad 3-STATE Buffer |

| 74126 | Fairchild Semiconductor | Quad 3-STATE Buffer |