M68Z512

Description

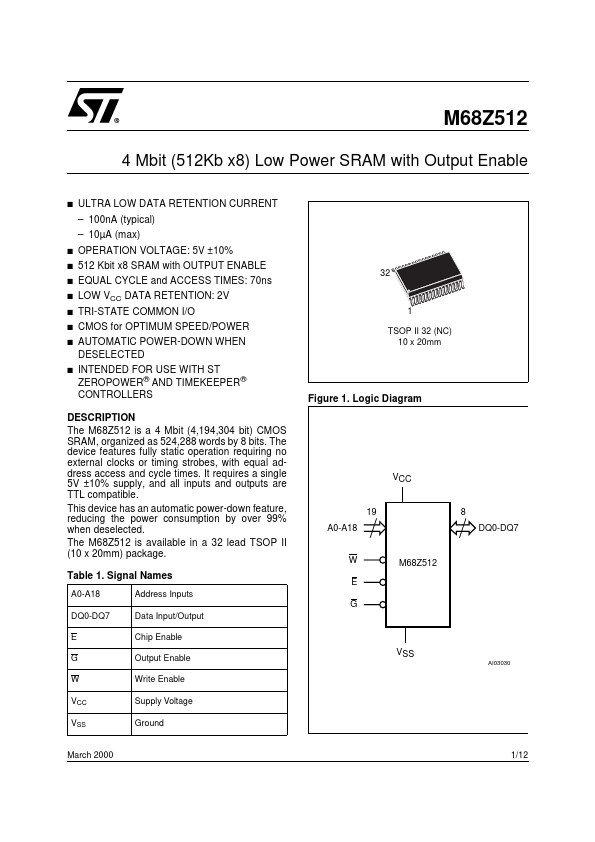

The M68Z512 is a 4 Mbit (4,194,304 bit) CMOS SRAM, organized as 524,288 words by 8 bits.

Key Features

- Signal Names

- Except for the rating "Operating Temperature Range", stresses above those listed in the Table "

- Up to a maximum operating VCC of 5.5V only

- One output at a time, not to exceed 1 second duration

- TSOP Connections

- Operating Modes

- X = VIH or VIL