| Part | M8813F1Y |

|---|---|

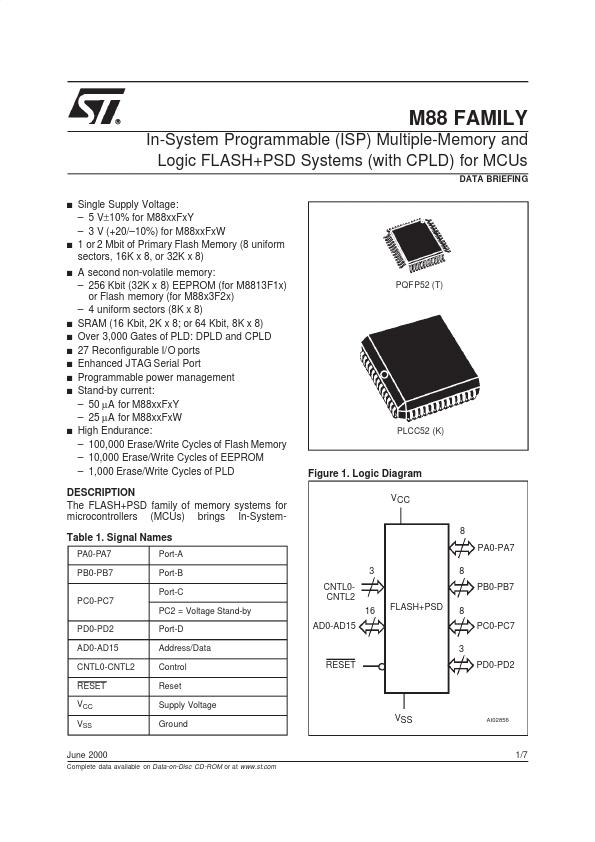

| Description | In-System Programmable ISP Multiple-Memory/Logic |

| Manufacturer | STMicroelectronics |

| Size | 54.24 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| GL3510-52 | Genesys Logic | USB 3.1 Gen 1 Hub Controller |

| MAC97A6 | KCD | 0.8A Logic level TRIAC |

| CS43198 | Cirrus Logic | 32-Bit High-Performance DAC |