SPC560P60L5 Overview

Key Specifications

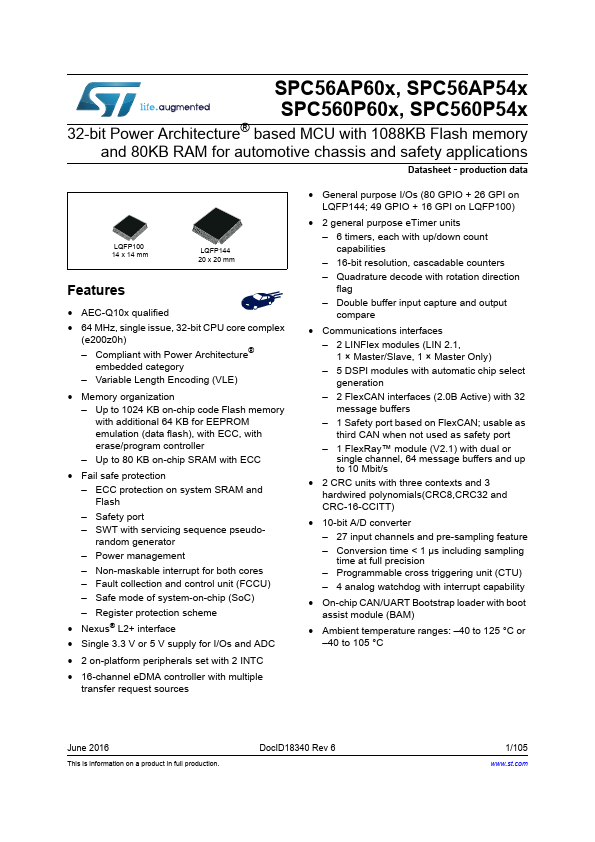

Package: LFQFP

Mount Type: Surface Mount

Pins: 144

Operating Voltage: 5 V

Key Features

- AEC-Q10x qualified

- Nexus® L2+ interface

- Single 3.3 V or 5 V supply for I/Os and ADC

- 2 on-platform peripherals set with 2 INTC

- 16-channel eDMA controller with multiple transfer request sources