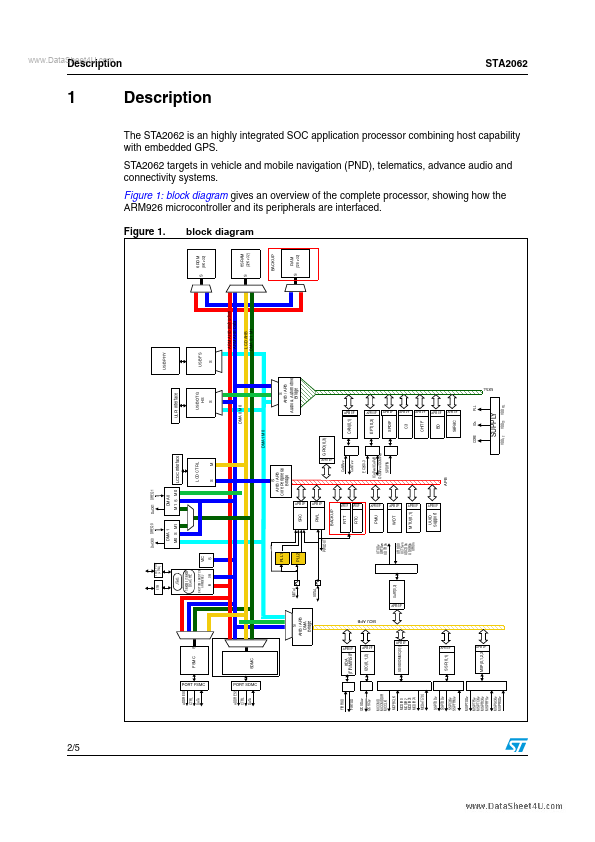

STA2062 Description

Figure 1. DREQ0 DREQ1 DMA 1 DMA 0 M1 S M0 LCDC Interface ULPI Interface JTAG 16 KB I / 16KB DCACHE USB PHY M0 S M1 ADDRESS CTRL FSMC LCD CTRL VIC (8K x 32) 8K ITCM / 8K DTCM ARM926EJ S USB OTG HS USB FS S S eROM S Description.

STA2062 Key Features

- High performance ARM926 MCU (up to 333MHz) MCU memory organization

- Cache: 16KByte instruction, 16KByte data

- 8KByte instruction TCM (tightly coupled memory)

- 8KByte data TCM

- 32KByte embedded ROM for boot

- Two banks of 64KByte embedded SRAM

- 512Byte embedded SRAM for back-up

- 4GByte total linear address space

- Memory extension through: Flexible static memory controller-FSMC (NOR/NAND Flash, CF/CF+, ROM, SRAM support) Mobile DDR/

- 64-channel interrupt controller (VIC)