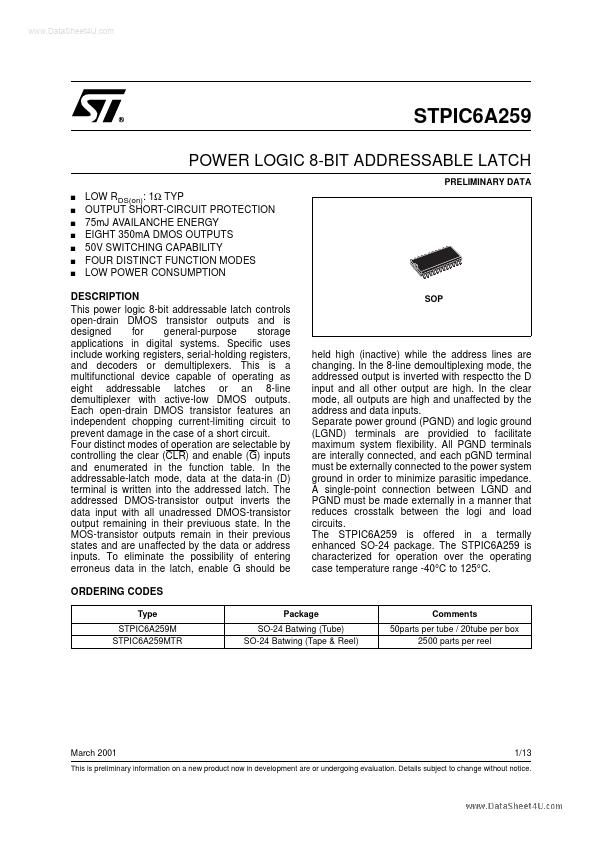

| Part | STPIC6A259 |

|---|---|

| Description | POWER LOGIC 8-BIT ADDRESSABLE LATCH |

| Manufacturer | STMicroelectronics |

| Size | 294.70 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SS41F | SEC | Hall Latch Position Sensor |

| 9314 | National Semiconductor | Quad Latch |

| U18 | Unisonic Technologies | BIPOLAR LATCH TYPE HALL-EFFECT |