Datasheet Summary

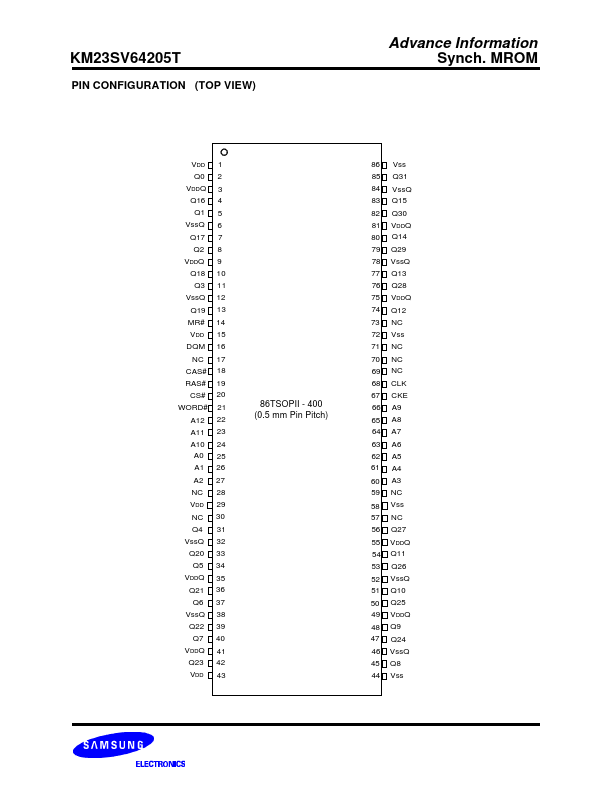

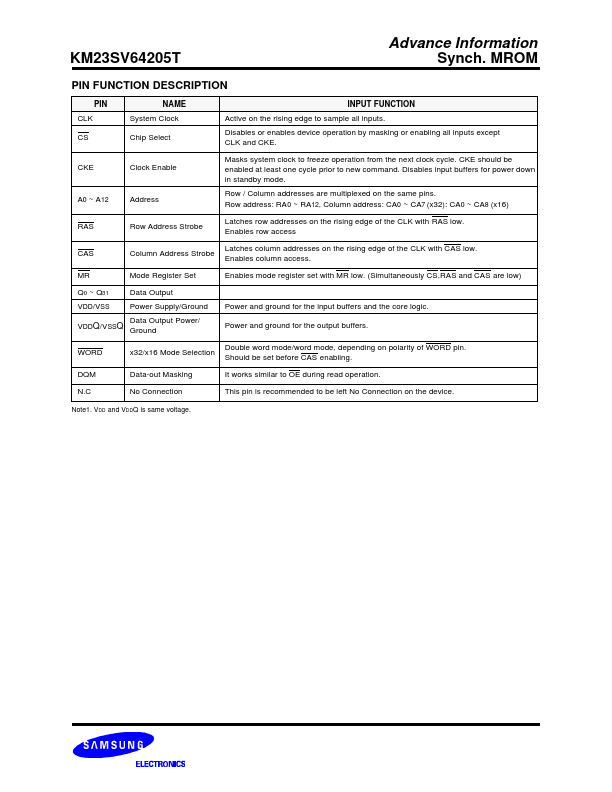

2Mx32 Synchronous MASKROM

Features

- JEDEC standard 3.3V power supply

- LVTTL patible with multiplexed address

- Address: Row address: RA0 ~ RA12 Column address: CA0 ~ CA7 (x32): CA0 ~ CA8 (x16)

- Switchable organization 4,194,304 x 16(word mode) / 2,097,152 x 32(double word mode)

- All inputs are sampled at the rising edge of the system clock

- Read Performance at memory point of view @33MHz 4-1-1-1 (RAS Latency=1, CAS Latency=3) @50MHz 5-1-1-1 (RAS Latency=1, CAS Latency=4) @66MHz 5-1-1-1 (RAS Latency=1, CAS Latency=4) @83MHz 7-1-1-1 (RAS Latency=2, CAS Latency=5) @100MHz 7-1-1-1 (RAS Latency=2, CAS Latency=5)

- tSAC : 6ns

- MRS cycle with address key programs -. RAS...