HYB39S16160CT-7

HYB39S16160CT-7 is 1M x 16 MBit Synchronous DRAM manufactured by Siemens Semiconductor Group.

- Part of the HYB39S16160CT-6 comparator family.

- Part of the HYB39S16160CT-6 comparator family.

..

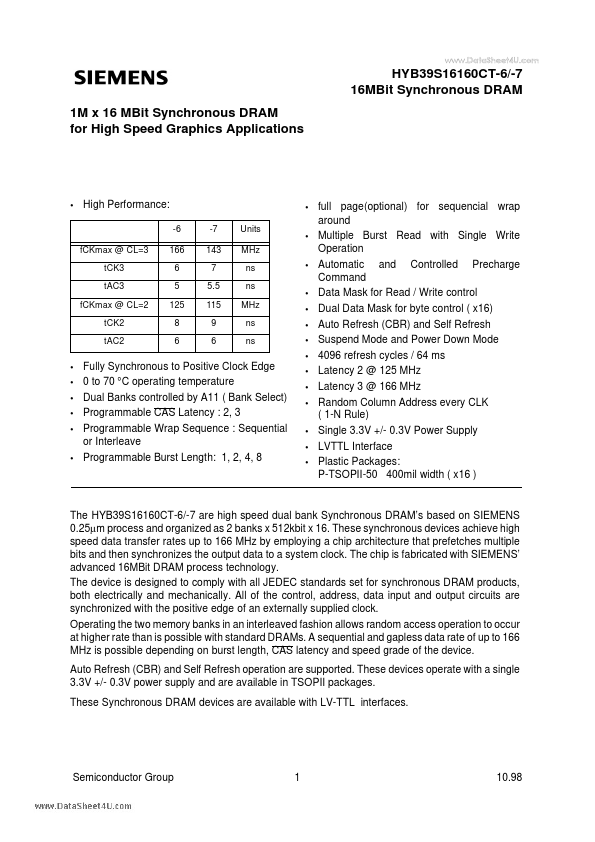

HYB39S16160CT-6/-7 16MBit Synchronous DRAM 1M x 16 MBit Synchronous DRAM for High Speed Graphics Applications

- High Performance:

-6 fCKmax @ CL=3 tCK3 tAC3 fCKmax @ CL=2 tCK2 tAC2 166 6 5 125 8 6 -7 143 7 5.5 115 9 6 Units MHz ns ns MHz ns ns

- -

- -

- -

- - full page(optional) for sequencial wrap around Multiple Burst Read with Single Write Operation Automatic mand and Controlled Precharge

Data Mask for Read / Write control Dual Data Mask for byte control ( x16) Auto Refresh (CBR) and Self Refresh Suspend Mode and Power Down Mode 4096 refresh cycles / 64 ms Latency 2 @ 125 MHz Latency 3 @ 166 MHz Random Column Address every CLK ( 1-N Rule) Single 3.3V +/-...