SI53342

feature typical ultra-low jitter of 50 fs and operate over a wide frequency range from dc to 1250 MHz. Built-in LDOs deliver high PSRR performance and reduces the need for external ponents simplifying low jitter clock distribution in noisy environments.

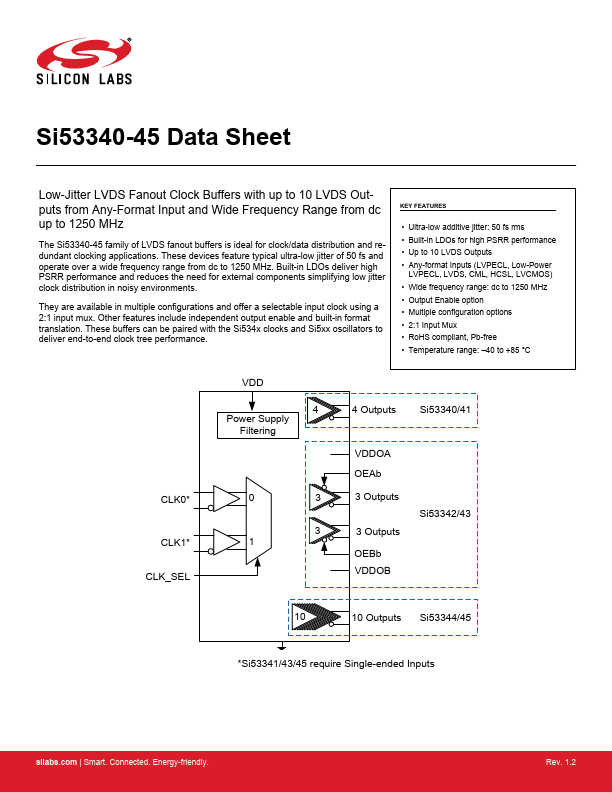

They are available in multiple configurations and offer a selectable input clock using a 2:1 input mux. Other features include independent output enable and built-in format translation. These buffers can be paired with the Si534x clocks and Si5xx oscillators to deliver end-to-end clock tree performance.

KEY FEATURES

- Ultra-low additive jitter: 50 fs rms

- Built-in LDOs for high PSRR performance

- Up to 10 LVDS Outputs

- Any-format Inputs (LVPECL, Low-Power

LVPECL, LVDS, CML, HCSL, LVCMOS)

- Wide frequency range: dc to 1250 MHz

- Output Enable option

- Multiple configuration options

- 2:1 Input Mux

- Ro HS pliant, Pb-free

- Temperature range:

- 40 to +85 °C

CLK0- CLK1- CLK_SEL

Power Supply Filtering

03 3

4 Outputs...