Si5348

Si5348 is Network Synchronizer manufactured by Skyworks Solutions.

Si5348 Rev E Data Sheet

Network Synchronizer for Sync E/ 1588 PTP Tele Boundary (T-BC) and Slave (T-SC) Clocks

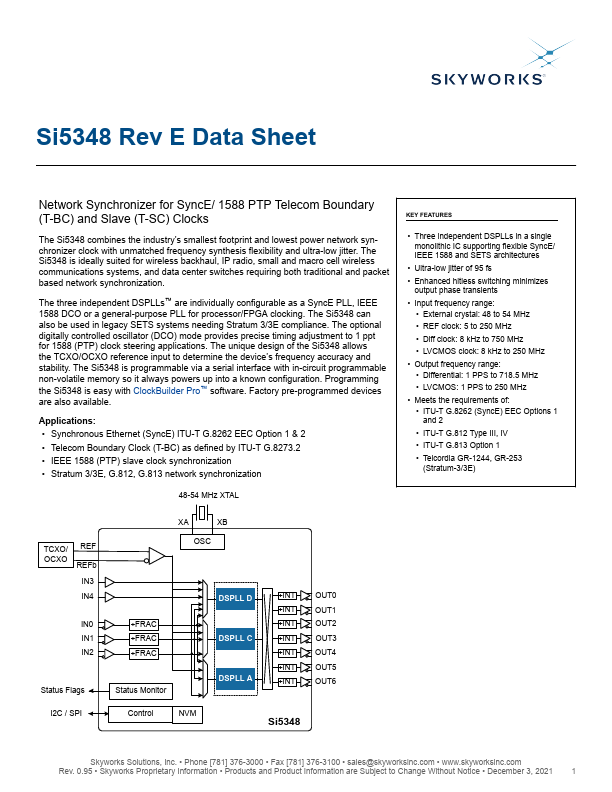

The Si5348 bines the industry’s smallest footprint and lowest power network synchronizer clock with unmatched frequency synthesis flexibility and ultra-low jitter. The Si5348 is ideally suited for wireless backhaul, IP radio, small and macro cell wireless munications systems, and data center switches requiring both traditional and packet based network synchronization.

The three independent DSPLLs™ are individually configurable as a Sync E PLL, IEEE 1588 DCO or a general-purpose PLL for processor/FPGA clocking. The Si5348 can also be used in legacy SETS systems needing Stratum 3/3E pliance. The optional digitally controlled oscillator (DCO) mode provides precise timing adjustment to 1 ppt for 1588 (PTP) clock steering applications. The unique design of the Si5348 allows the TCXO/OCXO reference input to determine the device’s frequency accuracy and stability. The Si5348 is programmable via a serial interface with in-circuit programmable non-volatile memory so it always powers up into a known configuration. Programming the Si5348 is easy with Clock Builder Pro™ software. Factory pre-programmed devices are also available.

Applications:

- Synchronous Ethernet (Sync E) ITU-T G.8262 EEC Option 1 & 2

- Tele Boundary Clock (T-BC) as defined by ITU-T G.8273.2

- IEEE 1588 (PTP) slave clock synchronization

- Stratum 3/3E, G.812, G.813 network synchronization

48-54 MHz XTAL

KEY Features

- Three independent DSPLLs in a single monolithic IC supporting flexible Sync E/ IEEE 1588 and SETS architectures

- Ultra-low jitter of 95 fs

- Enhanced hitless switching minimizes output phase transients

- Input frequency range:

- External crystal: 48 to 54 MHz

- REF clock: 5 to 250 MHz

- Diff clock: 8 k Hz to 750 MHz

- LVCMOS clock: 8 k Hz to 250 MHz

- Output frequency range:

- Differential: 1 PPS to 718.5 MHz

- LVCMOS: 1 PPS to 250 MHz

- Meets the requirements of:

- ITU-T...