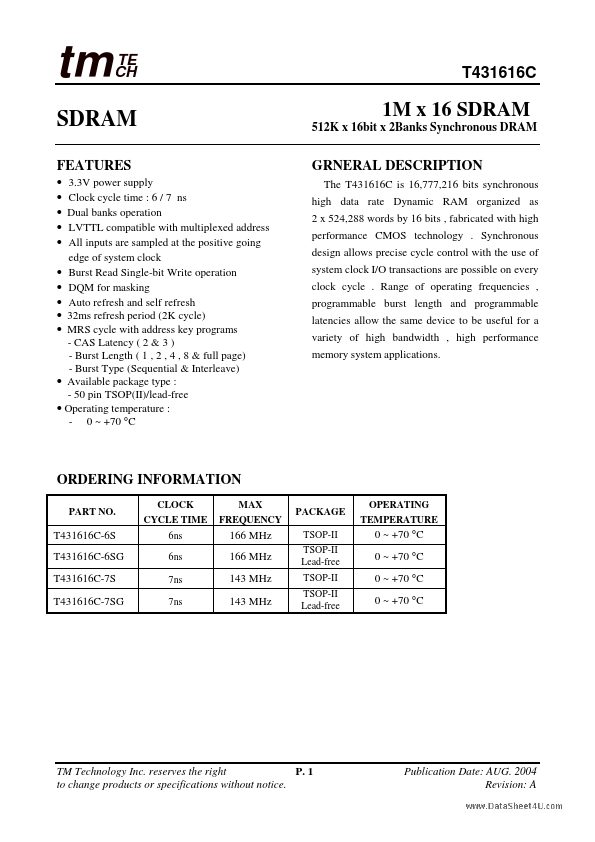

T431616C

T431616C is 1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM manufactured by TMT.

tm

- -

- -

- TE CH

SDRAM

Features

3.3V power supply Clock cycle time : 6 / 7 ns Dual banks operation LVTTL patible with multiplexed address All inputs are sampled at the positive going edge of system clock

- Burst Read Single-bit Write operation

- DQM for masking

- Auto refresh and self refresh

- 32ms refresh period (2K cycle)

- MRS cycle with address key programs

- CAS Latency ( 2 & 3 )

- Burst Length ( 1 , 2 , 4 , 8 & full page)

- Burst Type (Sequential & Interleave)

- Available package type :

- 50 pin TSOP(II)/lead-free

- Operating temperature :

- 0 ~ +70 °C

1M x 16 SDRAM

512K x 16bit x 2Banks Synchronous DRAM

GRNERAL DESCRIPTION

The T431616C is 16,777,216 bits...