Datasheet Summary

..

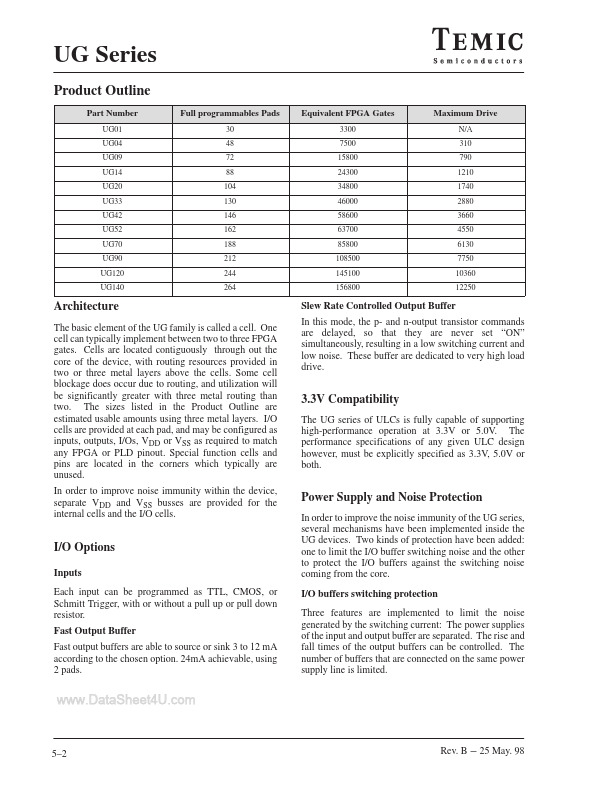

UG Series

0.6µm ULC Series

Description

The UG series of ULCs is well suited for conversion of medium- to-large sized CPLDs and FPGAs. Devices are implemented in high-performance CMOS technology with 0.6-µm (drawn) channel lengths, and are capable of supporting flip-flop toggle rates of 350 MHz, operating clock frequencies up to 150 MHz and input to output delays as fast as 5 ns. The architecture of the UG series allows for efficient conversion of many PLD architectures and FPGA device types. A pact RAM cell, along with the large number of available gates allows the implementation of RAM in FPGA architectures that support this feature, as well as JTAG boundary-scan...