TS25L16APP Description

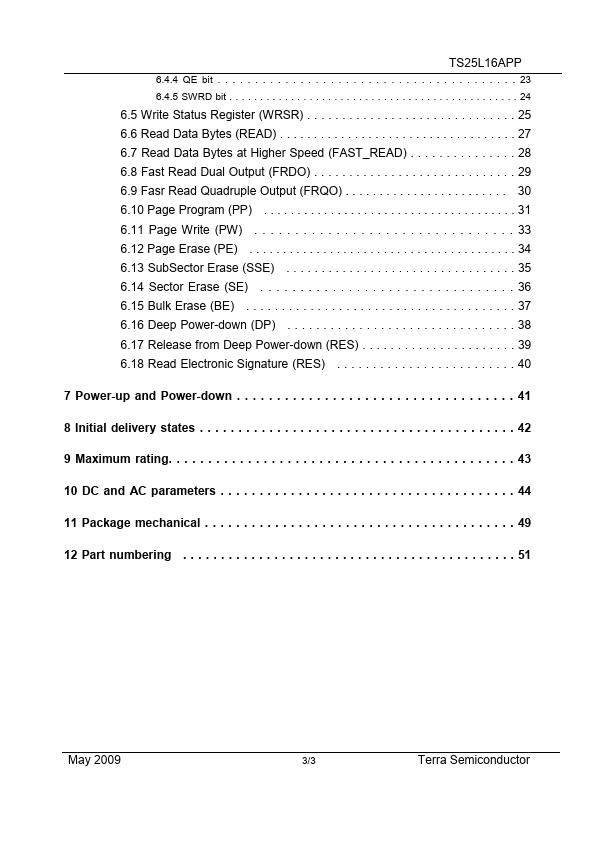

6 2 Signal descriptions . 8 2.1 Serial Data output (SO) SO1 . 8 2.2 Serial Data input (SI) SO0.

TS25L16APP Key Features

- Full voltage range: 2.7 to 3.6 V read and program operations

- 32ea sectors with 512 Kb each

- Page Program (up to 256 bytes) in 0.3 ms (typical)

- Page Write (up to 256 bytes) in 2.8 ms (typical)

- Program cycles are on a page by page basis

- 2ms typical Page Erase Time

- 2ms typical SubSector Erase Time

- 32ms typical Sector Erase time

- 1 sec typical Bulk Erase time

- 100,000 P/E cycles per sector typical