TC74HC155AF

TC74HC155AF is Dual 2-to-4 Line Decoder 3-to-8 Line Decoder manufactured by Toshiba.

features dual 1-to-4 line demultiplexers with individual strobe input (1G and 2G), individual data inputs (1C and 2C) and mon binary address inputs (A and B).

When both decoders are enabled by the strobes, the inverted output of 1C data and non-inverted output of 2C data will be brought to the selected output pins of each section.

A 1-to-8 line demultiplexer can be easily built up by providing a data signal to both the 1C and 2C inputs; the output order will be 1Y3 (MSB), 1Y2, 1Y1, 1Y0, 2Y3, 2Y2, 2Y1, 2Y0 (LSB).

This device can be used as a 2-to-4 line decoder or a 3-to-8 line decoder when 1C is held high and 2C is held low.

All inputs are equipped with protection circuits against static discharge or transient excess voltage.

Features

- High speed: tpd = 12 ns (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Output drive capability: 10 LSTTL loads

- Symmetrical output impedance: |IOH| = IOL = 4 m A (min)

- Balanced propagation delays: tp LH ∼- tp HL

- Wide operating voltage range: VCC (opr) = 2 to 6 V

- Pin and function patible with 74LS155

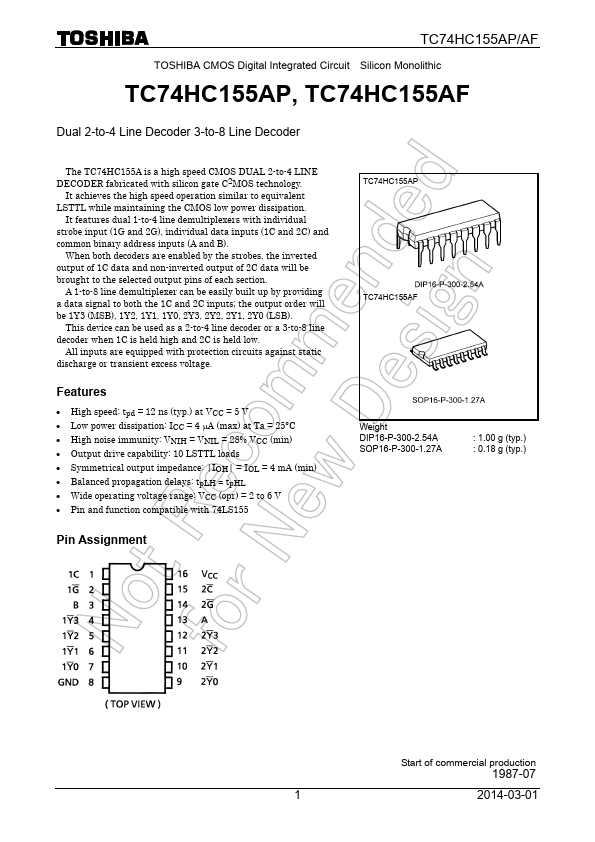

Pin Assignment

TC74HC155AP

Weight DIP16-P-300-2.54A SOP16-P-300-1.27A

: 1.00 g (typ.) : 0.18 g (typ.)

Start of mercial production

1987-07 1 2014-03-01

IEC Logic Symbol

TC74HC155AP/AF

Truth Table

Inputs B A 1G XXH LLL LHL HL L HH L XXX

X: Don’t care

Outputs 1C 1Y0 1Y1 1Y2 1Y3 XHHHH H L HHH HH L HH HHH L H HHHH L L HHHH

Inputs B A 2G XXH LLL LHL HL L HH L XXX

X: Don’t care

Outputs 2C 2Y0 2Y1 2Y2 2Y3 XHHHH L LHHH L H L HH L HH L H L HHH L HHHHH

2 2014-03-01

System Diagram

TC74HC155AP/AF

Absolute Maximum Ratings (Note 1)

Characteristics

Symbol

Rating

Unit

Supply voltage range DC input voltage DC output voltage Input diode current

VCC VIN VOUT IIK

- 0.5 to...