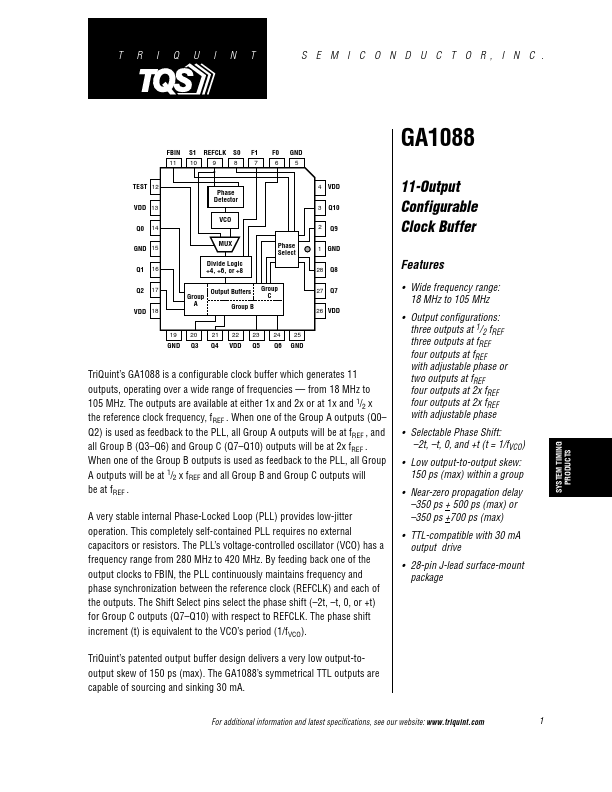

| Part | GA1088 |

|---|---|

| Description | 11-Output Configurable Clock Buffer |

| Manufacturer | TriQuint Semiconductor |

| Size | 207.35 KB |

Pricing from 44.2042 USD, available from Run Hong Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Run Hong Electronics | 6464 | 1+ : 44.2042 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| BUF04 | Analog Devices | Closed-Loop High Speed Buffer |

| 74HC125 | NXP Semiconductors | Quad buffer/line driver |

| BUF03 | Analog Devices | High Speed Voltage Follower/Buffer |