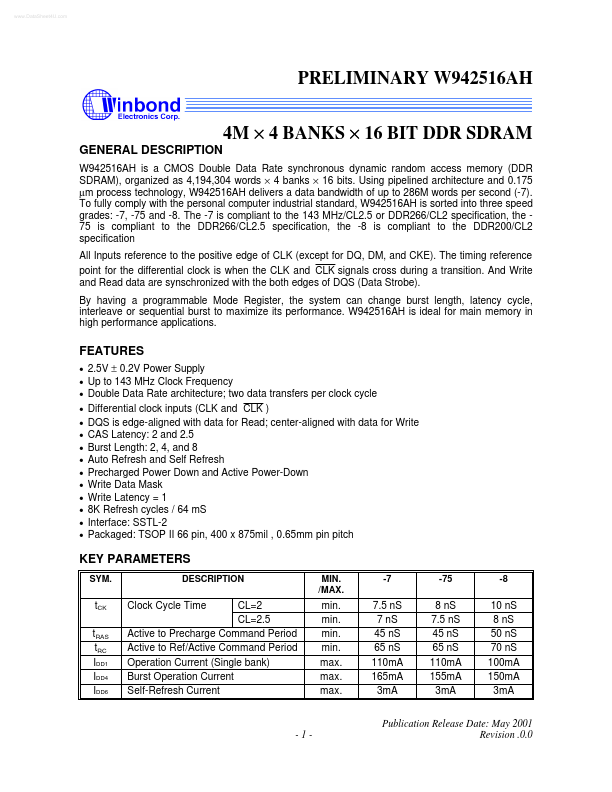

W942516AH

W942516AH is DDR SDRAM manufactured by Winbond.

DESCRIPTION

W942516AH is a CMOS Double Data Rate synchronous dynamic random access memory (DDR SDRAM), organized as 4,194,304 words × 4 banks × 16 bits. Using pipelined architecture and 0.175 µm process technology, W942516AH delivers a data bandwidth of up to 286M words per second (-7). To fully ply with the personal puter industrial standard, W942516AH is sorted into three speed grades: -7, -75 and -8. The -7 is pliant to the 143 MHz/CL2.5 or DDR266/CL2 specification, the 75 is pliant to the DDR266/CL2.5 specification, the -8 is pliant to the DDR200/CL2 specification All Inputs reference to the positive edge of CLK (except for DQ, DM, and CKE). The timing reference point for the differential clock is when the CLK and CLK signals cross during a transition. And Write and Read data are synschronized with the both edges of DQS (Data Strobe). By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W942516AH is ideal for main memory in high performance applications.

FEATURES

- 2.5V ± 0.2V Power Supply

- Up to 143 MHz Clock Frequency

- Double Data Rate architecture; two data transfers per clock cycle

- Differential clock inputs (CLK and CLK )

- DQS is edge-aligned with data for Read; center-aligned with data for Write

- CAS Latency: 2 and 2.5

- Burst Length: 2, 4, and 8

- Auto Refresh and Self Refresh

- Precharged Power Down and Active Power-Down

- Write Data Mask

- Write Latency = 1

- 8K Refresh cycles / 64 m S

- Interface: SSTL-2

- Packaged: TSOP II 66 pin, 400 x 875mil , 0.65mm pin pitch

KEY PARAMETERS

SYM. DESCRIPTION

MIN. /MAX. -7 -75 -8 t CK t RAS t RC IDD1 IDD4 IDD6

Clock Cycle Time

CL=2 CL=2.5 Active to Precharge mand Period Active to Ref/Active mand Period Operation Current (Single bank) Burst Operation Current Self-Refresh Current min. min. min. min. max. max. max.

7.5 n S 7 n S 45 n S 65 n S 110m A 165m A 3m A

8 n S 7.5 n S 45 n S 65 n S 110m A 155m A 3m A

10 n S 8 n S 50 n S 70...