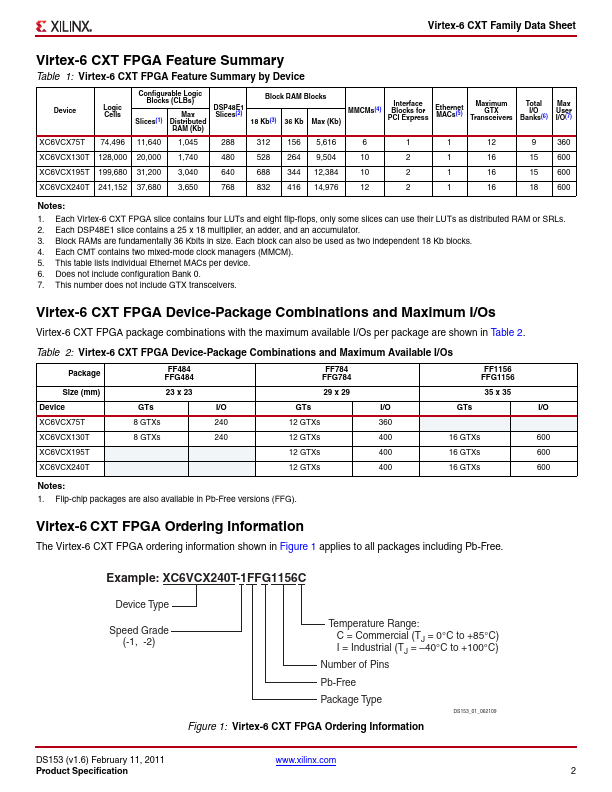

XC6VCX75T Description

Virtex®-6 CXT FPGAs provide designers needing power-optimized 3.75 Gb/s transceiver performance with an optimized ratio of built-in system-level blocks. These include 36 Kb block RAM/FIFOs, up to 15 Mb of block RAM, up to 768 DSP48E1 slices, enhanced mixed-mode clock management blocks, PCI Express® (GEN 1) patible integrated blocks, a tri-mode Ethernet media access controller (MAC), up to 241K logic cells, and...

XC6VCX75T Key Features

- Advanced, high-performance, FPGA Logic

- Real 6-input look-up table (LUT) technology

- Dual LUT5 (5-input LUT) option