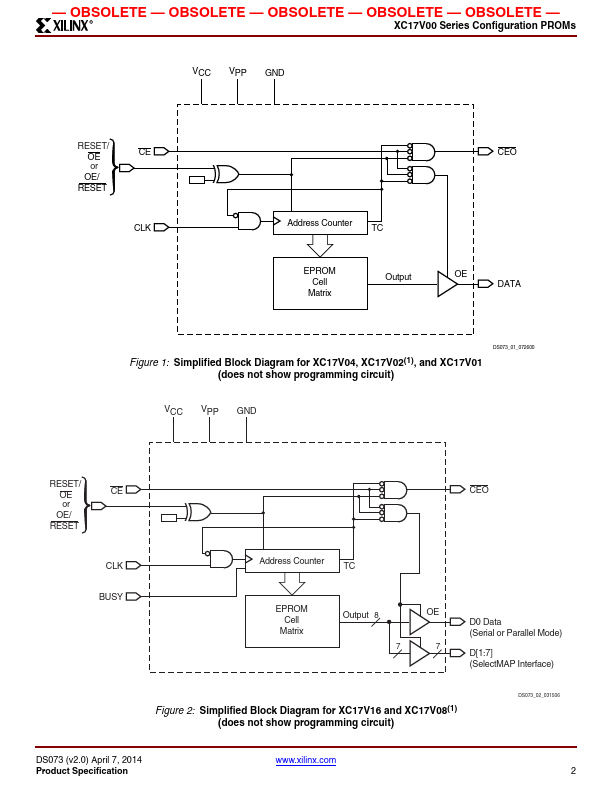

XC17V02 Description

Xilinx.

XC17V02 Key Features

- One-time programmable (OTP) read-only memory designed to store configuration bitstreams of Xilinx® FPGA devices

- Simple interface to the FPGA

- Cascadable for storing longer or multiple bitstreams

- Programmable reset polarity (active High or active

- Low-power CMOS floating-gate process

- 3.3V supply voltage

- Guaranteed 20 year life data retention

- Available in pact plastic packages: VQ44, PC44, PC20, VO8, and SO20(1)

- Programming support by leading programmer manufacturers

- Design support using the ISE® Foundation™ and ISE WebPACK™ software