XCV400 Description

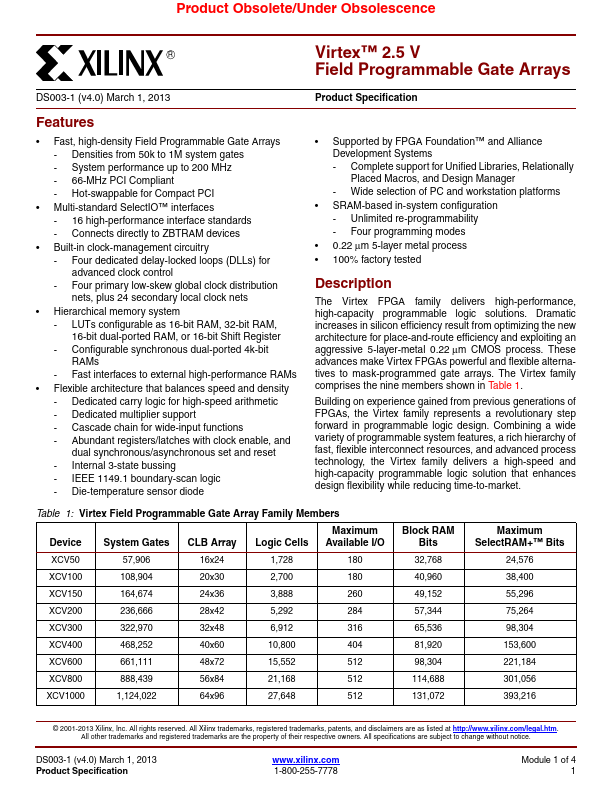

The Virtex FPGA family delivers high-performance, high-capacity programmable logic solutions. Dramatic increases in silicon efficiency result from optimizing the new architecture for place-and-route efficiency and exploiting an aggressive 5-layer-metal 0.22 µm CMOS process. These advances make Virtex FPGAs powerful and flexible alternatives to mask-programmed gate arrays.

XCV400 Key Features

- Fast, high-density Field-Programmable Gate Arrays

- Densities from 50k to 1M system gates

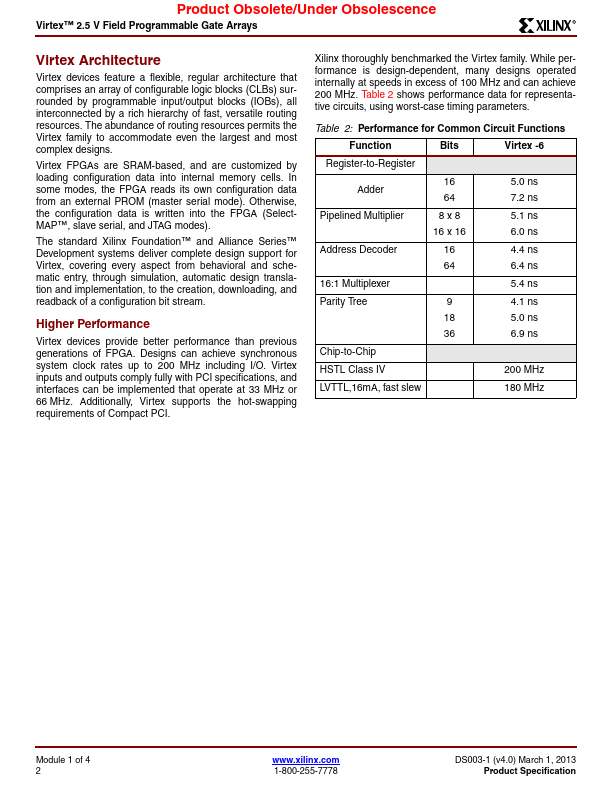

- System performance up to 200 MHz

- 66-MHz PCI pliant

- Hot-swappable for pact PCI Multi-standard SelectIO™ interfaces

- 16 high-performance interface standards

- Connects directly to ZBTRAM devices Built-in clock-management circuitry

- Four dedicated delay-locked loops (DLLs) for advanced clock control

- Four primary low-skew global clock distribution nets, plus 24 secondary local clock nets Hierarchical memory system

- LUTs configurable as 16-bit RAM, 32-bit RAM, 16-bit dual-ported RAM, or 16-bit Shift Register