XCV50E

Overview

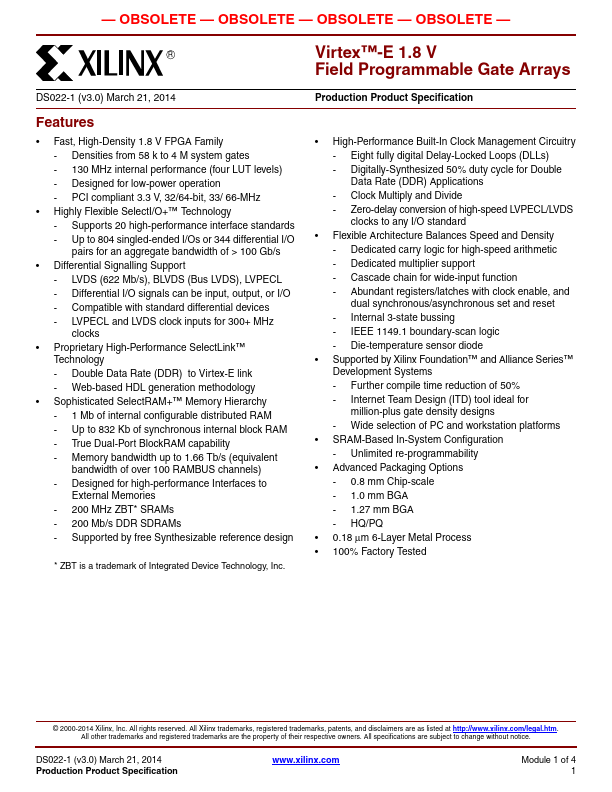

- Fast, High-Density 1.8 V FPGA Family - Densities from 58 k to 4 M system gates - 130 MHz internal performance (four LUT levels) - Designed for low-power operation - PCI compliant 3.3 V, 32/64-bit, 33/ 66-MHz Highly Flexible SelectI/O+™ Technology - Supports 20 high-performance interface standards - Up to 804 singled-ended I/Os or 344 differential I/O pairs for an aggregate bandwidth of > 100 Gb/s Differential Signalling Support - LVDS (622 Mb/s), BLVDS (Bus LVDS), LVPECL - Differential I/O signals can be input, output, or I/O - Compatible with standard differential devices - LVPECL and LVDS clock inputs for 300+ MHz clocks Proprietary High-Performance SelectLink™ Technology - Double Data Rate (DDR) to Virtex-E link - Web-based HDL generation methodology Sophisticated SelectRAM+™ Memory Hierarchy - 1 Mb of internal configurable distributed RAM - Up to 832 Kb of synchronous internal block RAM - True Dual-Port BlockRAM capability - Memory bandwidth up to 1.66 Tb/s (equivalent bandwidth of over 100 RAMBUS channels) - Designed for high-performance Interfaces to External Memories - 200 MHz ZBT* SRAMs - 200 Mb/s DDR SDRAMs - Supported by free Synthesizable reference design

- ZBT is a trademark of Integrated Device Technology, Inc. * * * * * * * * * *

- High-Performance Built-In Clock Management Circuitry - Eight fully digital Delay-Locked Loops (DLLs) - Digitally-Synthesized 50% duty cycle for Double Data Rate (DDR) Applications - Clock Multiply and Divide - Zero-delay conversion of high-speed LVPECL/LVDS clocks to any I/O standard Flexible Architecture Balances Speed and Density - Dedicated carry logic for high-speed arithmetic - Dedicated multiplier support - Cascade chain for wide-input function - Abundant registers/latches with clock enable, and dual synchronous/asynchronous se