PDSP16116MC Overview

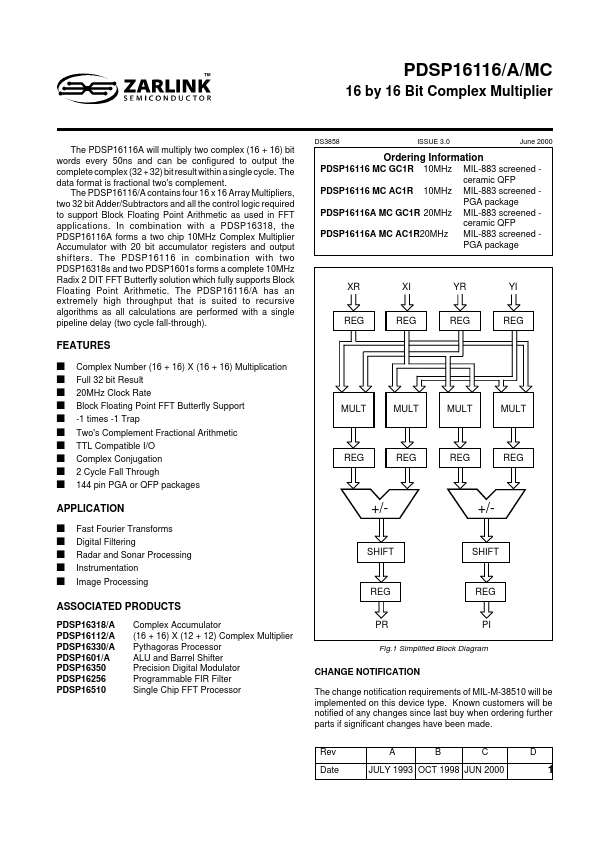

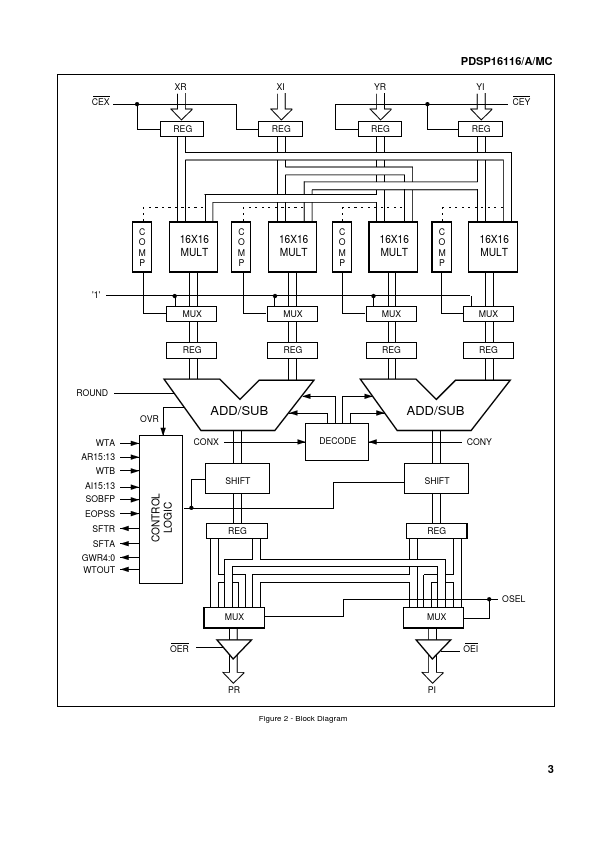

The data format is fractional two's plement. The PDSP16116/A contains four 16 x 16 Array Multipliers, two 32 bit Adder/Subtractors and all the control logic required to support Block Floating Point Arithmetic as used in FFT applications. In bination with a PDSP16318, the PDSP16116A forms a two chip 10MHz plex Multiplier Accumulator with 20 bit accumulator registers and output shifters.