54ACT11138 Overview

Key Specifications

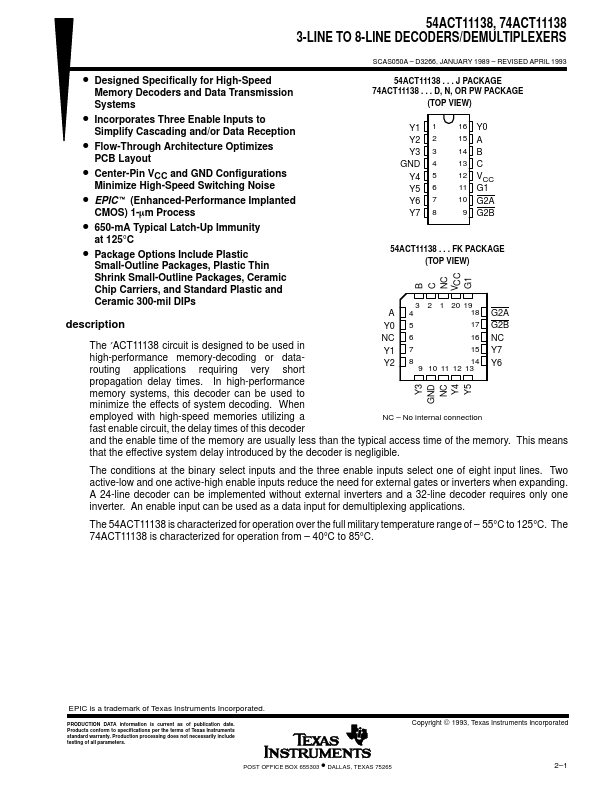

Description

Y0 5 17 G2B The ′ACT11138 circuit is designed to be used in high-performance memory-decoding or datarouting applications requiring very short NC 6 16 NC Y1 7 15 Y7 Y2 8 14 9 10 11 12 13 Y6 propagation delay times. In high-performance Y3 GND NC Y4 Y5 memory systems, this decoder can be used to minimize the effects of system decoding.