74AC11379

Overview

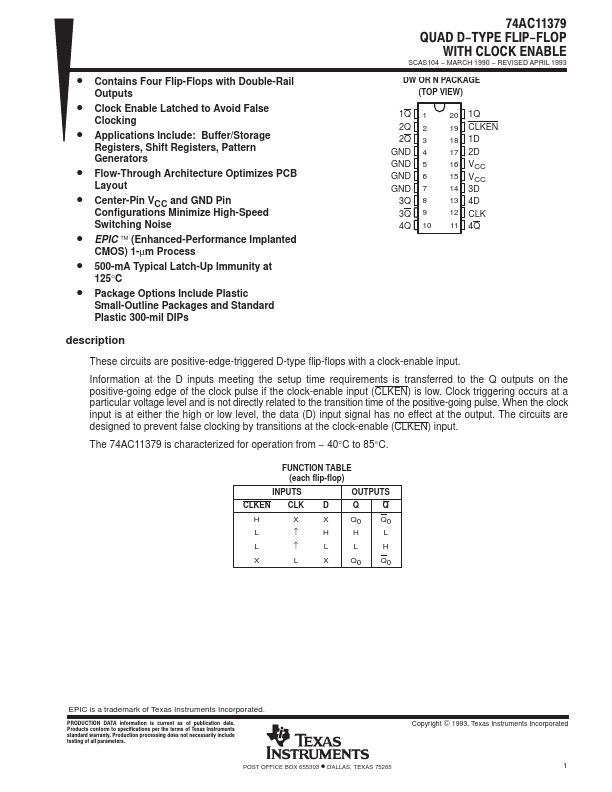

These circuits are positive-edge-triggered D-type flip-flops with a clock-enable input. Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse if the clock-enable input (CLKEN) is low.