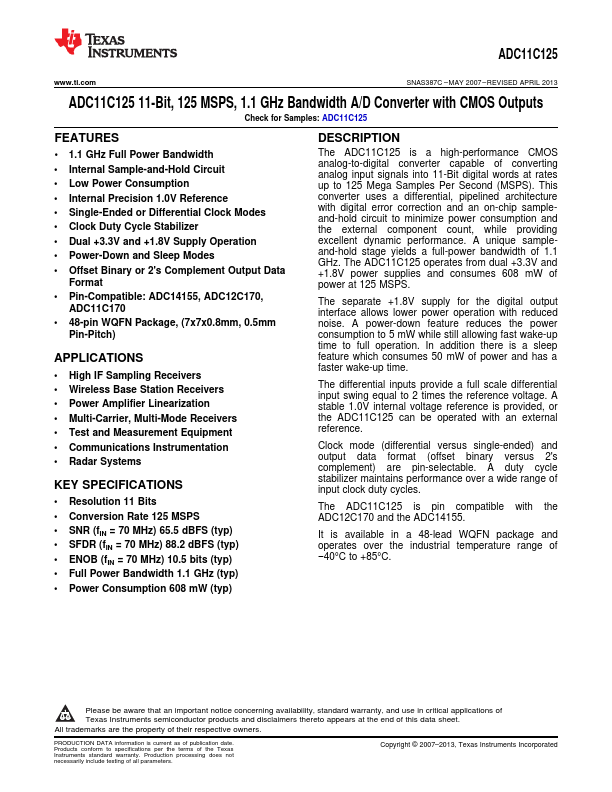

ADC11C125 Overview

Description

The ADC11C125 is a high-performance CMOS analog-to-digital converter capable of converting analog input signals into 11-Bit digital words at rates up to 125 Mega Samples Per Second (MSPS). This converter uses a differential, pipelined architecture with digital error correction and an on-chip sampleand-hold circuit to minimize power consumption and the external component count, while providing excellent dynamic performance.

Key Features

- 2 1.1 GHz Full Power Bandwidth

- Internal Sample-and-Hold Circuit

- Low Power Consumption

- Internal Precision 1.0V Reference

- Single-Ended or Differential Clock Modes

- Clock Duty Cycle Stabilizer

- Dual +3.3V and +1.8V Supply Operation

- Power-Down and Sleep Modes

- Offset Binary or 2's Complement Output Data Format

- Pin-Compatible: ADC14155, ADC12C170, ADC11C170