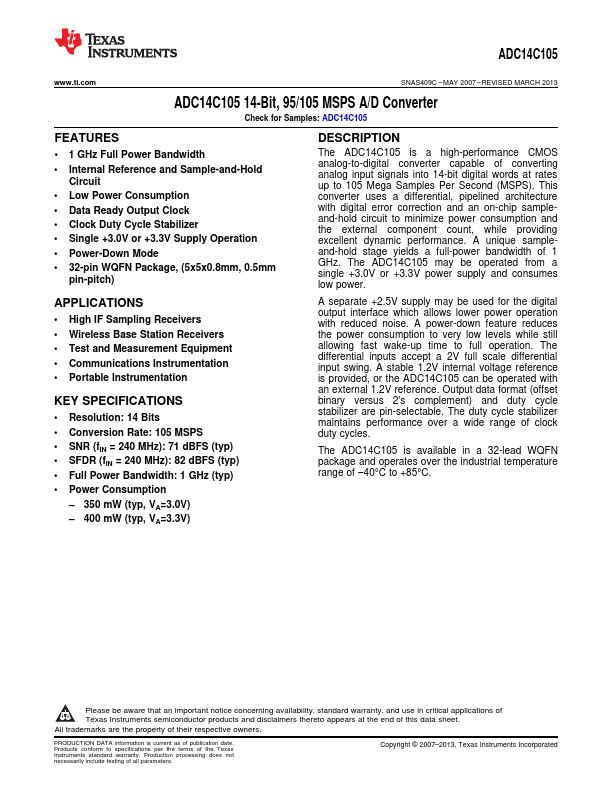

ADC14C105

FEATURES

- 2 1 GHz Full Power Bandwidth

- Internal Reference and Sample-and-Hold

Circuit

- Low Power Consumption

- Data Ready Output Clock

- Clock Duty Cycle Stabilizer

- Single +3.0V or +3.3V Supply Operation

- Power-Down Mode

- 32-pin WQFN Package, (5x5x0.8mm, 0.5mm pin-pitch)

APPLICATIONS

- High IF Sampling Receivers

- Wireless Base Station Receivers

- Test and Measurement Equipment

- munications Instrumentation

- Portable Instrumentation

KEY SPECIFICATIONS

- Resolution: 14 Bits

- Conversion Rate: 105 MSPS

- SNR (f IN = 240 MHz): 71 d BFS (typ)

- SFDR (f IN = 240 MHz): 82 d BFS (typ)

- Full Power Bandwidth: 1 GHz (typ)

- Power Consumption

- 350 m W (typ, VA=3.0V)

- 400 m W (typ, VA=3.3V)

DESCRIPTION

The ADC14C105 is a high-performance CMOS analog-to-digital converter capable of converting analog input signals into 14-bit digital words at rates up to 105 Mega Samples Per Second (MSPS). This converter uses a differential, pipelined architecture with digital error correction and an...