ADC32J25

Overview

The ADC32J2x is a high-linearity, ultra-low power, dual-channel, 12-bit, 50-MSPS to 160-MSPS, analogto-digital converter (ADC) family. The devices are designed specifically to support demanding, high input frequency signals with large dynamic range requirements.

- 1 Dual Channel

- 12-Bit Resolution

- Single 1.8-V Supply

- Flexible Input Clock Buffer with Divide-by-1, -2, -4

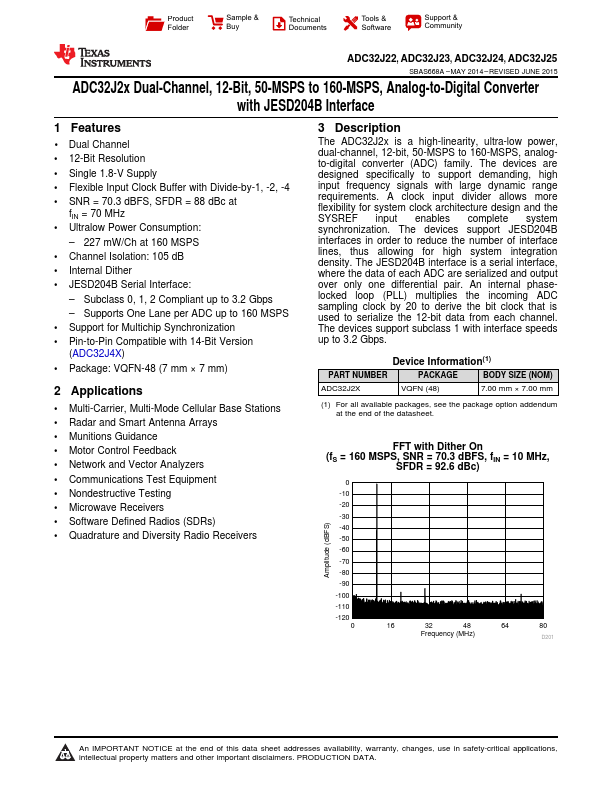

- SNR = 70.3 dBFS, SFDR = 88 dBc at fIN = 70 MHz

- Ultralow Power Consumption: - 227 mW/Ch at 160 MSPS

- Channel Isolation: 105 dB

- Internal Dither

- JESD204B Serial Interface: - Subclass 0, 1, 2 Compliant up to 3.2 Gbps - Supports One Lane per ADC up to 160 MSPS

- Support for Multichip Synchronization