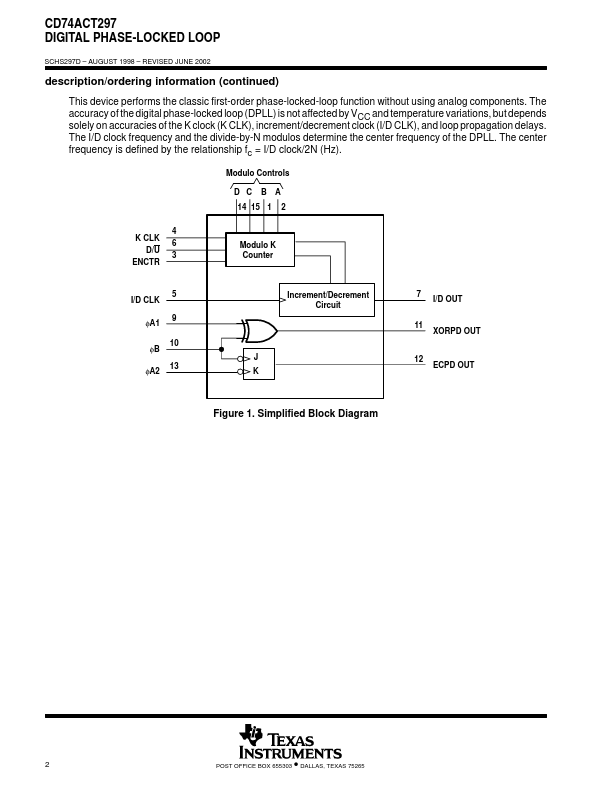

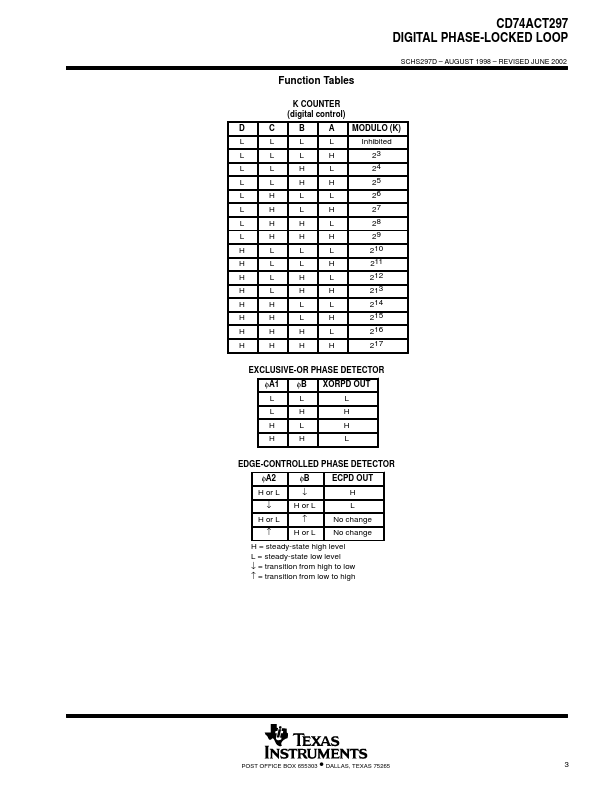

Datasheet Summary

CD74ACT297 DIGITAL PHASE-LOCKED LOOP

D Speed of Bipolar FCT, AS, and S, With

Significantly Reduced Power Consumption

D Digital Design Avoids Analog pensation Errors

D Easily Cascadable for Higher-Order Loops D Useful Frequency Range

- DC to 110 MHz Typical (K CLK)

- DC to 70 MHz Typical (I/D CLK)

D Dynamically Variable Bandwidth D Very Narrow Bandwidth Attainable D Power-On Reset D Output Capability

- Standard: XORPD OUT, ECPD OUT

- Bus Driver: I/D OUT

D SCR Latch-Up-Resistant CMOS Process and Circuit Design

D Balanced Propagation Delays D ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015

SCHS297D

- AUGUST 1998

- REVISED JUNE 2002

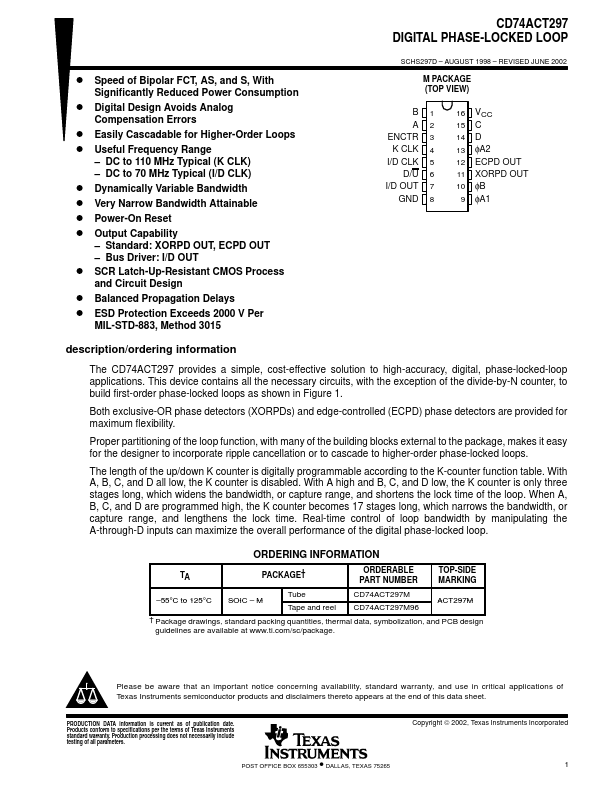

M PACKAGE (TOP VIEW)

B1 A2 ENCTR 3 K CLK 4...