Datasheet Summary

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

Reference Design

SCAS862G

- NOVEMBER 2008

- REVISED JULY 2016

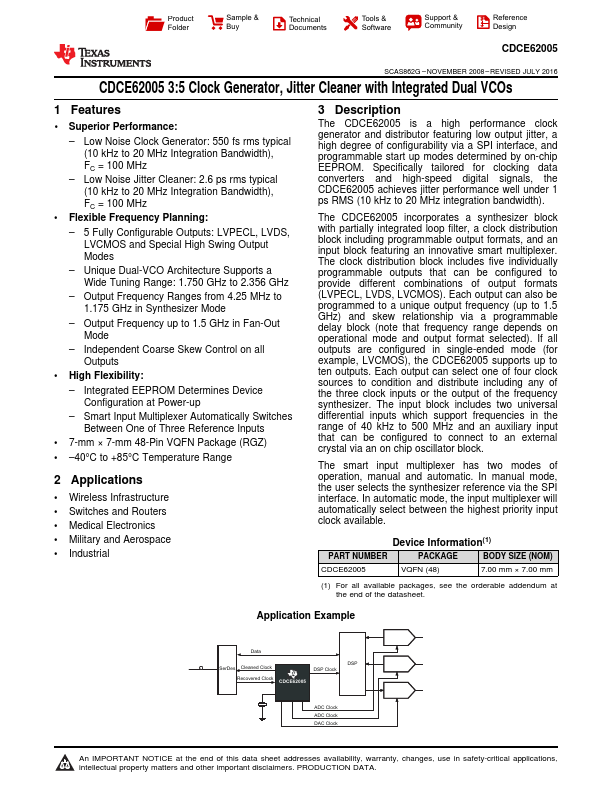

CDCE62005 3:5 Clock Generator, Jitter Cleaner with Integrated Dual VCOs

1 Features

- 1 Superior Performance:

- Low Noise Clock Generator: 550 fs rms typical (10 kHz to 20 MHz Integration Bandwidth), FC = 100 MHz

- Low Noise Jitter Cleaner: 2.6 ps rms typical (10 kHz to 20 MHz Integration Bandwidth), FC = 100 MHz

- Flexible Frequency Planning:

- 5 Fully Configurable Outputs: LVPECL, LVDS, LVCMOS and Special High Swing Output Modes

- Unique Dual-VCO Architecture Supports a Wide Tuning Range: 1.750 GHz to 2.356 GHz

- Output...