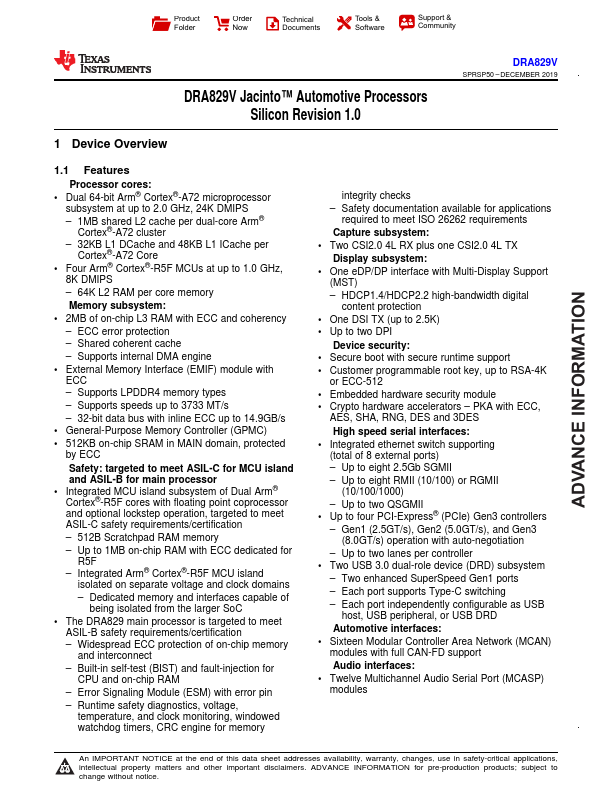

DRA829V Overview

Key Features

- Four Arm® Cortex®-R5F MCUs at up to 1.0 GHz, 8K DMIPS – 64K L2 RAM per core memory Memory subsystem

- 2MB of on-chip L3 RAM with ECC and coherency – ECC error protection – Shared coherent cache – Supports internal DMA engine

- General-Purpose Memory Controller (GPMC)

- 512KB on-chip SRAM in MAIN domain, protected by ECC Safety: targeted to meet ASIL-C for MCU island and ASIL-B for main processor