GC5328 Description

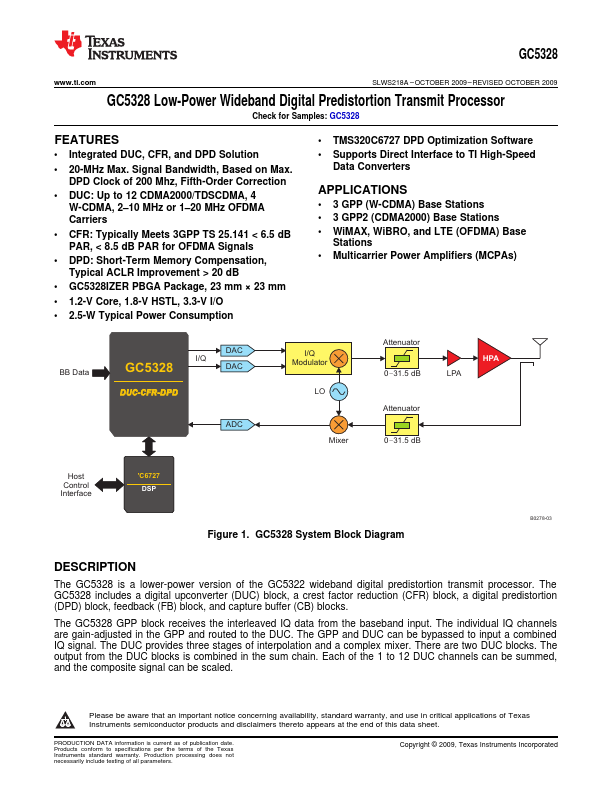

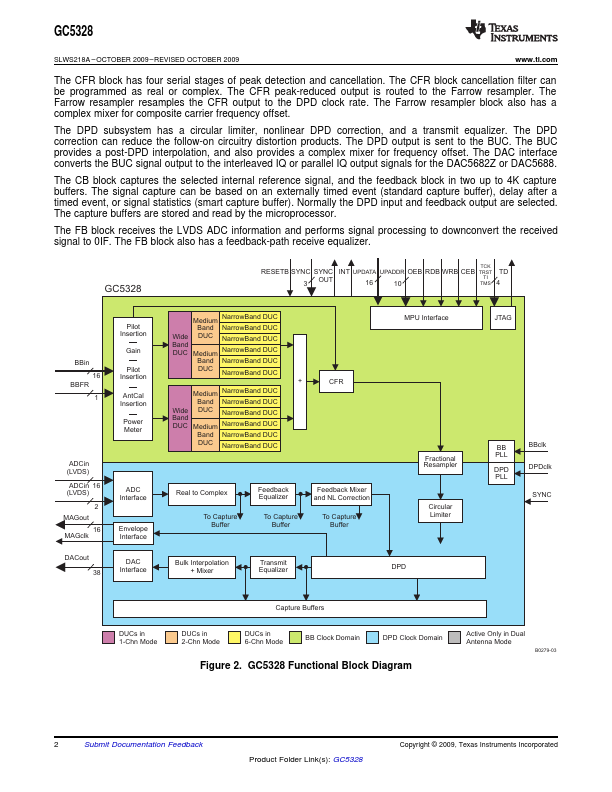

The GC5328 is a lower-power version of the GC5322 wideband digital predistortion transmit processor. The GC5328 includes a digital upconverter (DUC) block, a crest factor reduction (CFR) block, a digital predistortion (DPD) block, feedback (FB) block, and capture buffer (CB) blocks. The GC5328 GPP block receives the interleaved IQ data from the baseband input.

GC5328 Key Features

- Integrated DUC, CFR, and DPD Solution

- 20-MHz Max. Signal Bandwidth, Based on Max

- DUC: Up to 12 CDMA2000/TDSCDMA, 4

- CFR: Typically Meets 3GPP TS 25.141 < 6.5 dB PAR, < 8.5 dB PAR for OFDMA Signals

- DPD: Short-Term Memory pensation, Typical ACLR Improvement > 20 dB

- GC5328IZER PBGA Package, 23 mm × 23 mm

- 1.2-V Core, 1.8-V HSTL, 3.3-V I/O

- 2.5-W Typical Power Consumption

- TMS320C6727 DPD Optimization Software

- Supports Direct Interface to TI High-Speed