Datasheet Summary

.ti.

LMK04100, LMK04101, LMK04102, LMK04110 LMK04111, LMK04131, LMK04133

SNAS516B

- APRIL 2011

- REVISED NOVEMBER 2012

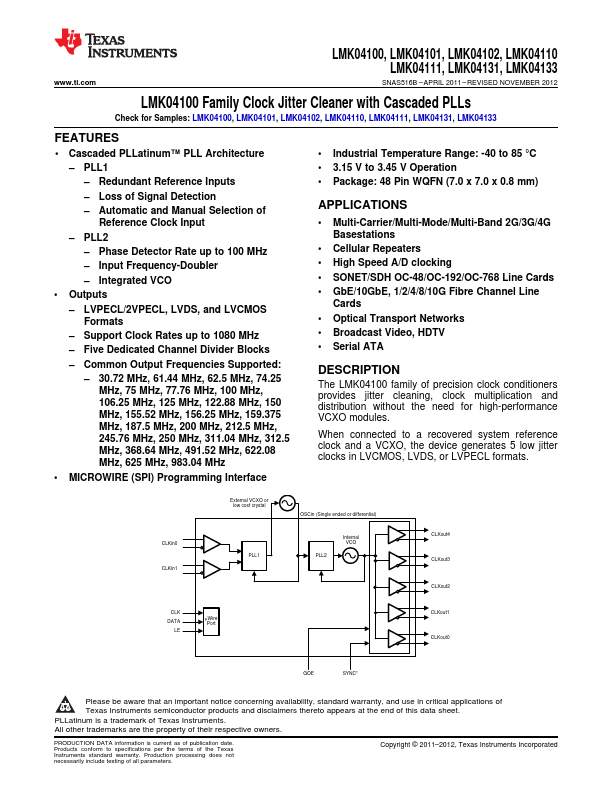

LMK04100 Family Clock Jitter Cleaner with Cascaded PLLs

Check for Samples: LMK04100, LMK04101, LMK04102, LMK04110, LMK04111, LMK04131, LMK04133

Features

- 23 Cascaded PLLatinum™ PLL Architecture

- PLL1

- Redundant Reference Inputs

- Loss of Signal Detection

- Automatic and Manual Selection of Reference Clock Input

- PLL2

- Phase Detector Rate up to 100 MHz

- Input Frequency-Doubler

- Integrated VCO

- Outputs

- LVPECL/2VPECL, LVDS, and LVCMOS Formats

- Support Clock Rates up to 1080 MHz

- Five Dedicated Channel Divider Blocks

- mon Output Frequencies Supported:

-...