LP2995 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 16

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 2.2 V

Description

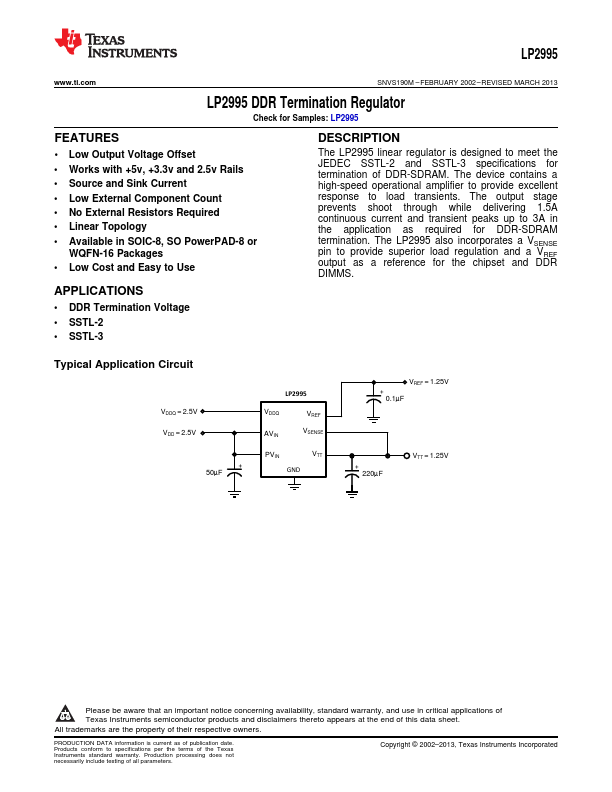

The LP2995 linear regulator is designed to meet the JEDEC SSTL-2 and SSTL-3 specifications for termination of DDR-SDRAM. The device contains a high-speed operational amplifier to provide excellent response to load transients.

Key Features

- 2 Low Output Voltage Offset

- Works with +5v, +3.3v and 2.5v Rails

- Source and Sink Current

- Low External Component Count

- No External Resistors Required