PGA112 Description

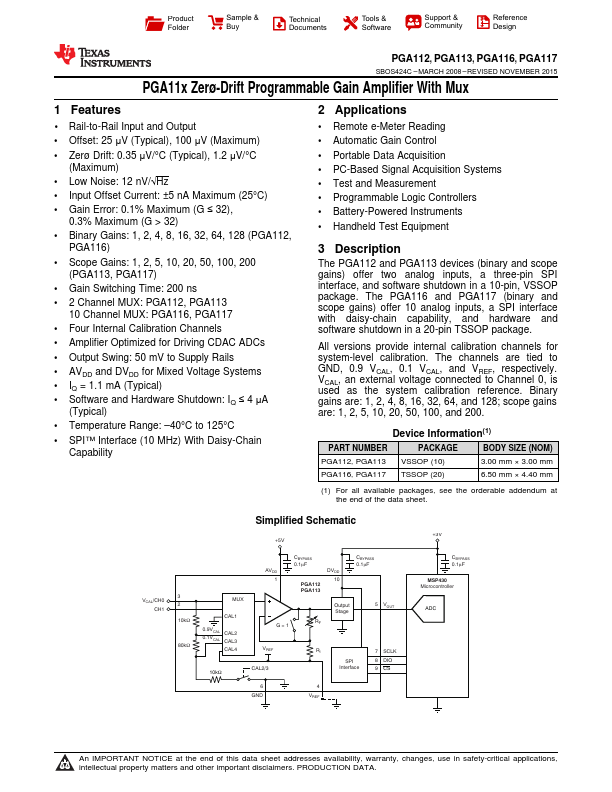

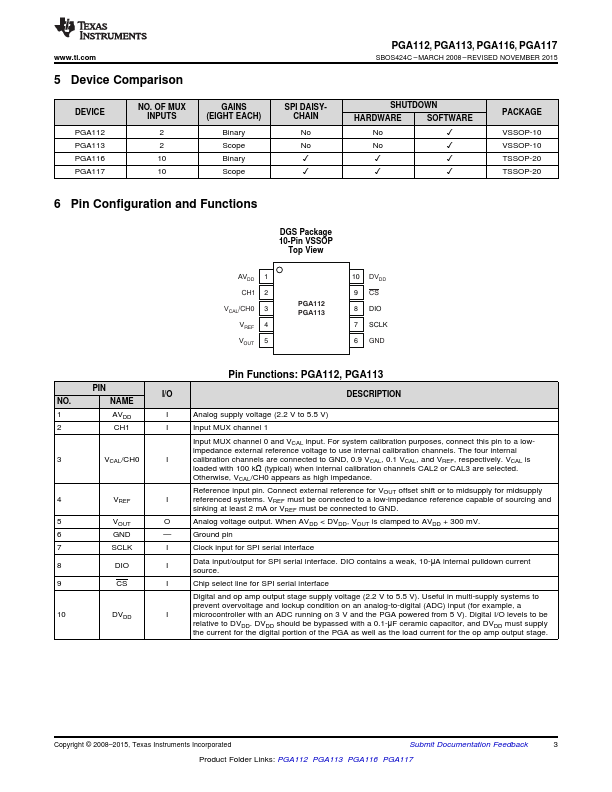

The PGA112 and PGA113 devices (binary and scope gains) offer two analog inputs, a three-pin SPI interface, and software shutdown in a 10-pin, VSSOP package. The PGA116 and PGA117 (binary and scope gains) offer 10 analog inputs, a SPI interface with daisy-chain capability, and hardware and software shutdown in a 20-pin TSSOP package. All versions provide internal calibration channels for system-level calibration.

PGA112 Key Features

- 1 Rail-to-Rail Input and Output

- Offset: 25 μV (Typical), 100 μV (Maximum)

- Zerø Drift: 0.35 μV/°C (Typical), 1.2 μV/°C

- Low Noise: 12 nV/√Hz

- Input Offset Current: ±5 nA Maximum (25°C)

- Gain Error: 0.1% Maximum (G ≤ 32)

- Binary Gains: 1, 2, 4, 8, 16, 32, 64, 128 (PGA112

- Scope Gains: 1, 2, 5, 10, 20, 50, 100, 200

- Gain Switching Time: 200 ns

- 2 Channel MUX: PGA112, PGA113