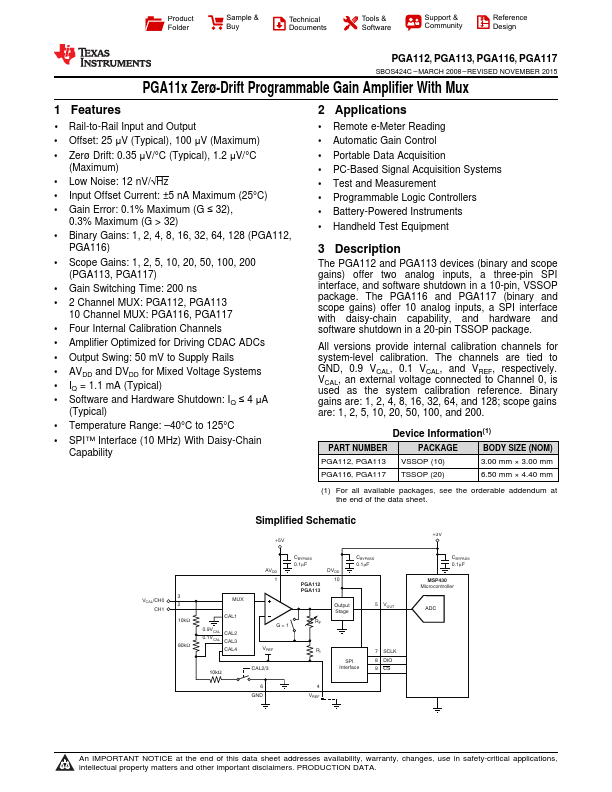

PGA113

Features

- 1 Rail-to-Rail Input and Output

- Offset: 25 μV (Typical), 100 μV (Maximum)

- Zerø Drift: 0.35 μV/°C (Typical), 1.2 μV/°C

(Maximum)

- Low Noise: 12 n V/√Hz

- Input Offset Current: ±5 n A Maximum (25°C)

- Gain Error: 0.1% Maximum (G ≤ 32),

0.3% Maximum (G > 32)

- Binary Gains: 1, 2, 4, 8, 16, 32, 64, 128 (PGA112,

PGA116)

- Scope Gains: 1, 2, 5, 10, 20, 50, 100, 200

(PGA113, PGA117)

- Gain Switching Time: 200 ns

- 2 Channel MUX: PGA112, PGA113

10 Channel MUX: PGA116, PGA117

- Four Internal Calibration Channels

- Amplifier Optimized for Driving CDAC ADCs

- Output Swing: 50 m V to Supply Rails

- AVDD and DVDD for Mixed Voltage Systems

- IQ = 1.1 m A (Typical)

- Software and Hardware Shutdown: IQ ≤ 4 μA

(Typical)

- Temperature Range:

- 40°C to 125°C

- SPI™ Interface (10 MHz) With Daisy-Chain

Capability

2 Applications

- Remote e-Meter Reading

- Automatic Gain Control

- Portable Data Acquisition

- PC-Based Signal Acquisition Systems

- Test and Measurement

- Programmable Logic...