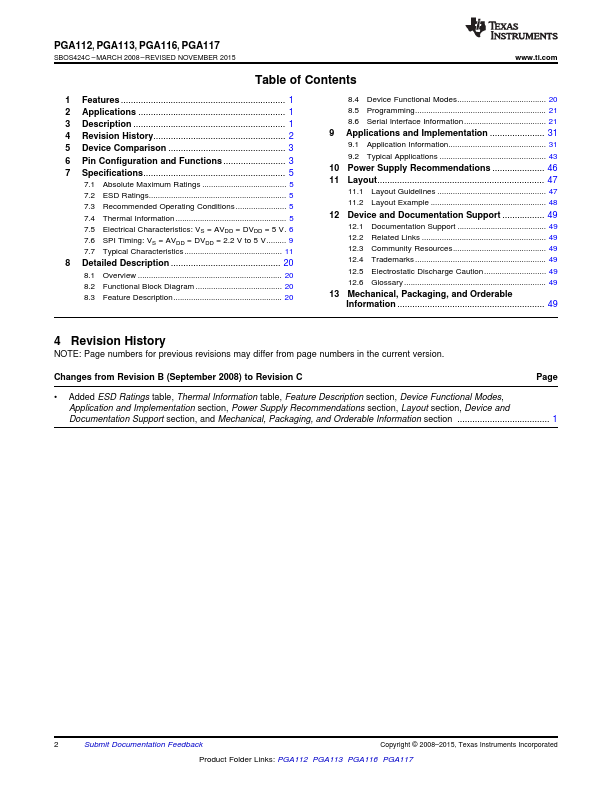

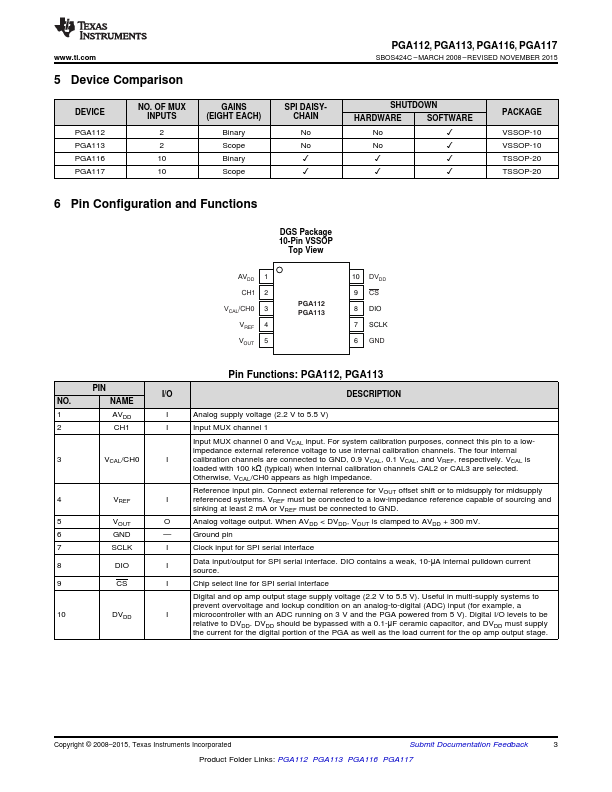

Datasheet Summary

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

Reference Design

PGA112, PGA113, PGA116, PGA117

SBOS424C

- MARCH 2008

- REVISED NOVEMBER 2015

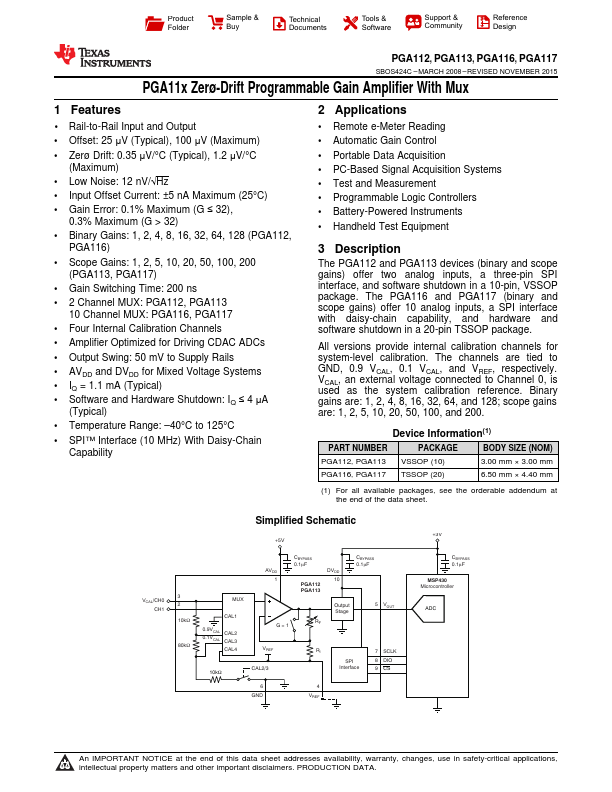

PGA11x Zerø-Drift Programmable Gain Amplifier With Mux

1 Features

- 1 Rail-to-Rail Input and Output

- Offset: 25 μV (Typical), 100 μV (Maximum)

- Zerø Drift: 0.35 μV/°C (Typical), 1.2 μV/°C

(Maximum)

- Low Noise: 12 nV/√Hz

- Input Offset Current: ±5 nA Maximum (25°C)

- Gain Error: 0.1% Maximum (G ≤ 32),

0.3% Maximum (G > 32)

- Binary Gains: 1, 2, 4, 8, 16, 32, 64, 128 (PGA112,

PGA116)

- Scope Gains: 1, 2, 5, 10, 20, 50, 100, 200

(PGA113, PGA117)

- Gain Switching Time: 200 ns

- 2 Channel MUX: PGA112,...