Datasheet Summary

.ti.

Features

- Members of the Texas Instruments Widebus™ Family

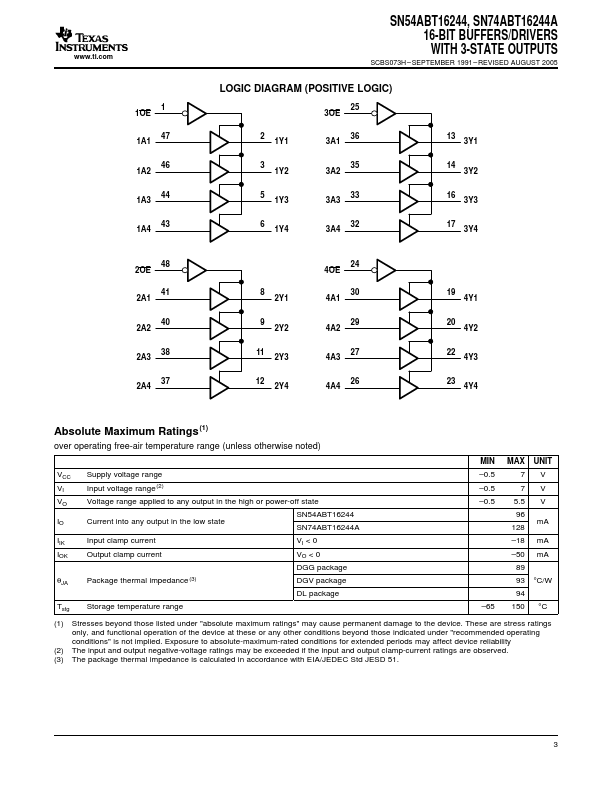

- State-of-the-Art EPIC-IIB™ BiCMOS Design Significantly Reduces Power Dissipation

- Latch-Up Performance Exceeds 500 mA Per JESD 70

- Typical VOLP (Output Ground Bounce) <1 V at VCC = 5 V, TA = 25°C

- Distributed VCC and GND Pin Configuration Minimizes High-Speed Switching Noise

- Flow-Through Architecture Optimizes PCB Layout

- High-Drive Outputs (- 32-mA IOH, 64-mA IOL)

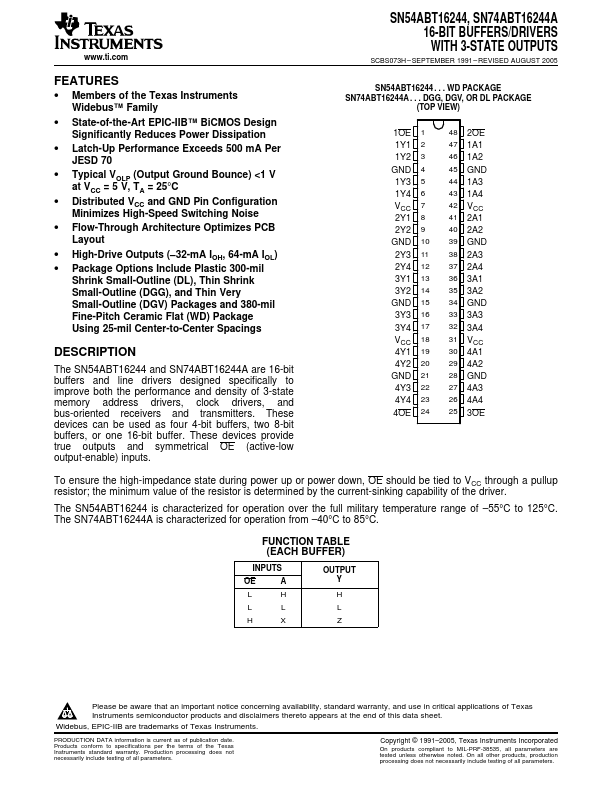

- Package Options Include Plastic 300-mil

Shrink Small-Outline (DL), Thin Shrink Small-Outline (DGG), and Thin Very Small-Outline (DGV) Packages and 380-mil Fine-Pitch Ceramic Flat (WD) Package Using 25-mil Center-to-Center Spacings

DESCRIPTION

The...