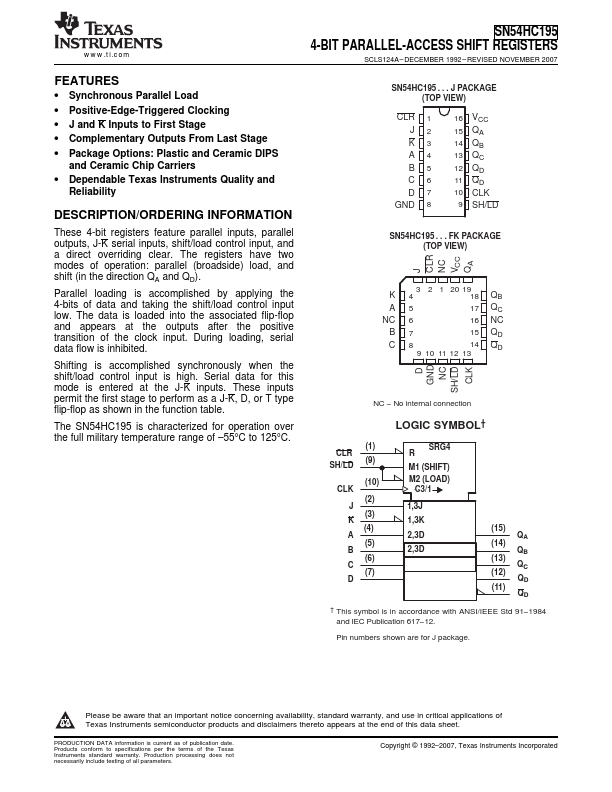

| Part | SN54HC195 |

|---|---|

| Description | 4-BIT PARALLEL-ACCESS SHIFT REGISTERS |

| Manufacturer | Texas Instruments |

| Size | 230.95 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HC165 | Texas Instruments | 8-Bit Parallel-Load Shift Registers |

| HM74HC595 | H&M Semiconductor | 8-Bit Shift Registers |

| 54HC164 | Texas Instruments | 8-Bit Parallel-Out Serial Shift Registers |