SN55LVDS32-SP

FEATURES

- QML-V Qualified, SMD 5962-97621

- Operate From a Single 3.3-V Supply

- Designed for Signaling Rates of up to 100

Mbps

- Differential Input Thresholds ±100 m V Max

- Typical Propagation Delay Times of 2.1 ns

- Power Dissipation 60 m W Typical Per Receiver at Maximum Data Rate

- Bus-Terminal ESD Protection Exceeds 8 k V

- Low-Voltage TTL (LVTTL) Logic Input Levels

- Open-Circuit Fail-Safe

- Cold Sparing for Space and High Reliability

Applications Requiring Redundancy

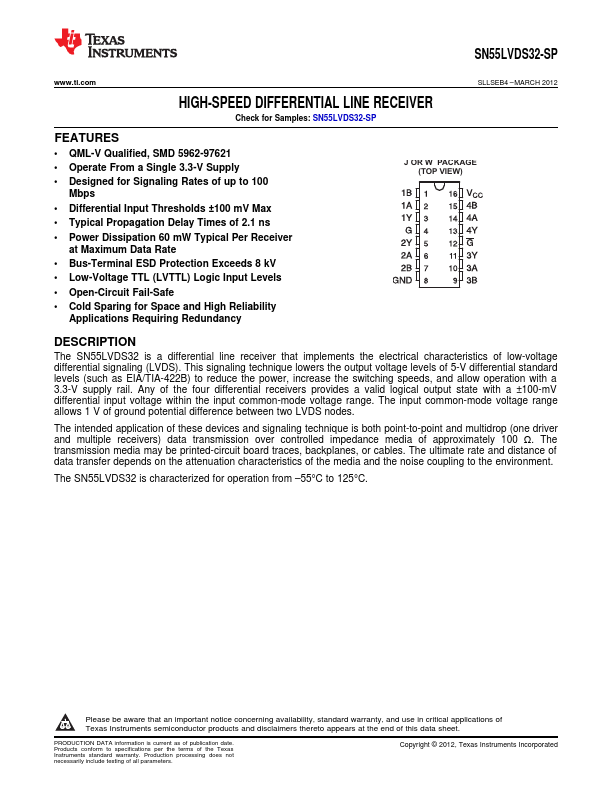

J OR W PACKAGE (TOP VIEW)

DESCRIPTION

The SN55LVDS32 is a differential line receiver that implements the electrical characteristics of low-voltage differential signaling (LVDS). This signaling technique lowers the output voltage levels of 5-V differential standard levels (such as EIA/TIA-422B) to reduce the power, increase the switching speeds, and allow operation with a 3.3-V supply rail. Any of the four differential receivers provides a valid logical output state with a ±100-m V differential input voltage...