SN65LVDS101

Features

- 1 Designed for Signaling Rates ≥ 2 Gbps

- Total Jitter < 65 ps

- Low-Power Alternative for the MC100EP16

- Low 100-ps (Maximum) Part-to-Part Skew

- 25 m V of Receiver Input Threshold Hysteresis

Over 0-V to 4-V Input Voltage Range

- Inputs Electrically patible With LVPECL,

CML, and LVDS Signal Levels

- 3.3-V Supply Operation

- LVDT Integrates 110-Ω Terminating Resistor

- Offered in SOIC and MSOP

2 Applications

- Wireless Infrastructure

- Tele Infrastructure

- Printers

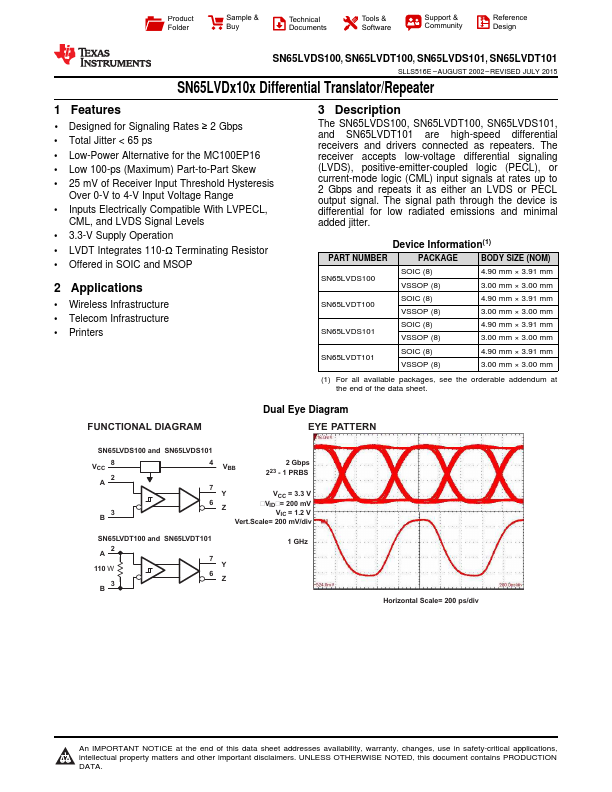

3 Description

The SN65LVDS100, SN65LVDT100, SN65LVDS101, and SN65LVDT101 are high-speed differential receivers and drivers connected as repeaters. The receiver accepts low-voltage differential signaling (LVDS), positive-emitter-coupled logic (PECL), or current-mode logic (CML) input signals at rates up to 2 Gbps and repeats it as either an LVDS or PECL output signal. The signal path through the device is differential for low radiated emissions and minimal added jitter.

Device Information(1)

PART...