SN74HC563 Overview

Description

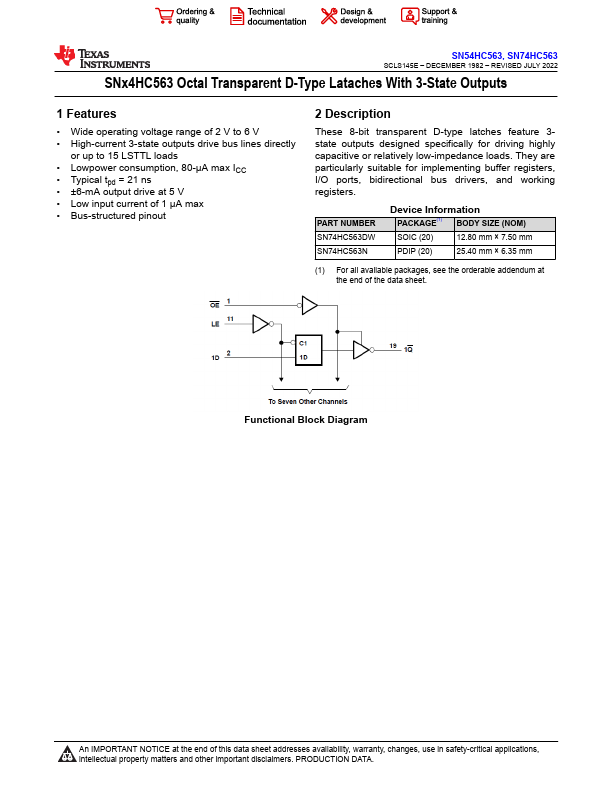

These 8-bit transparent D-type latches feature 3state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

Key Features

- Wide operating voltage range of 2 V to 6 V

- High-current 3-state outputs drive bus lines directly or up to 15 LSTTL loads

- Lowpower consumption, 80-μA max ICC

- Typical tpd = 21 ns

- ±6-mA output drive at 5 V

- Low input current of 1 μA max

- Bus-structured pinout