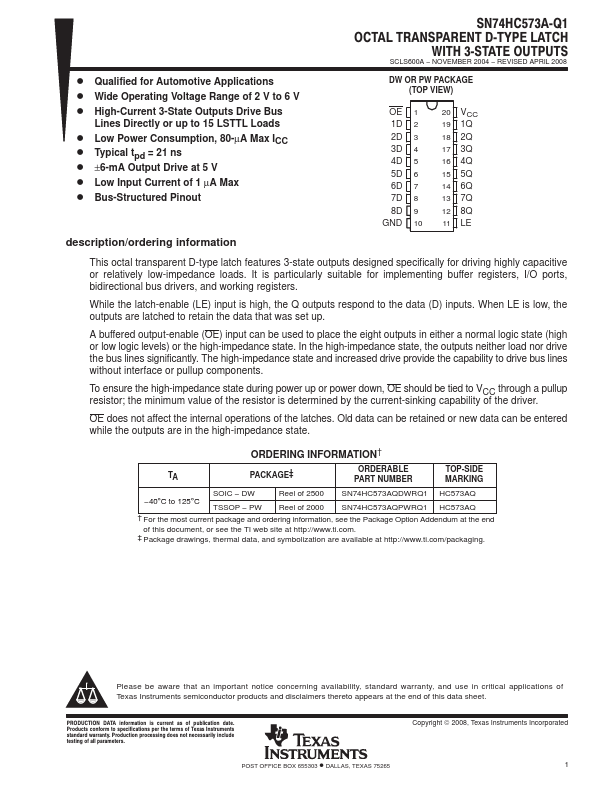

SN74HC573A-Q1 Overview

Key Specifications

Output Type (varies by manufacturer): CMOS

Key Features

- 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads

- It is particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers

- While the latch-enable (LE) input is high, the Q outputs respond to the data (D) inputs

- When LE is low, the outputs are latched to retain the data that was set up

- In the high-impedance state, the outputs neither load nor drive the bus lines significantly