| Part | SNJ54HC112W |

|---|---|

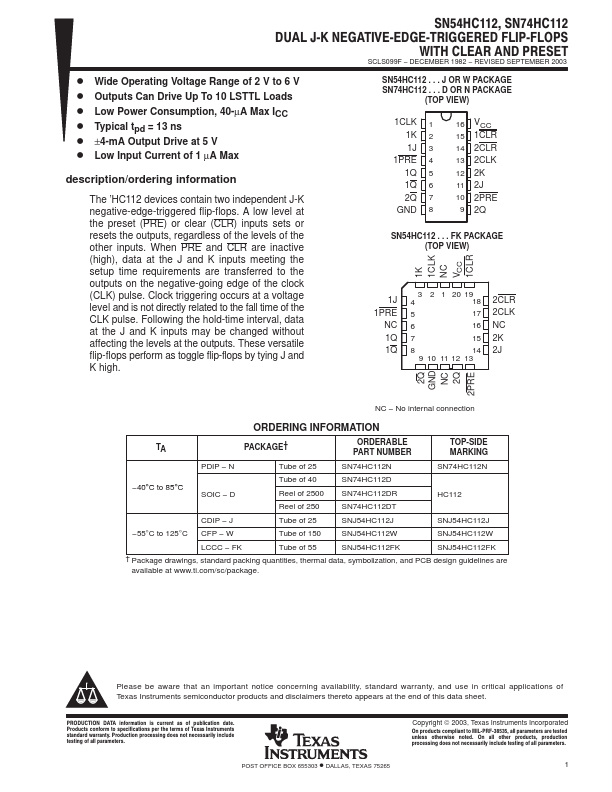

| Description | DUAL J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS |

| Manufacturer | Texas Instruments |

| Size | 1.01 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74LS74 | Hitachi Semiconductor | Dual D-type Positive Edge-triggered Flip-Flops |

| 7476 | Fairchild Semiconductor | Dual Master-Slave J-K Flip-Flops |

| 7474 | Fairchild Semiconductor | Dual Positive-Edge-Triggered D-Type Flip-Flops |