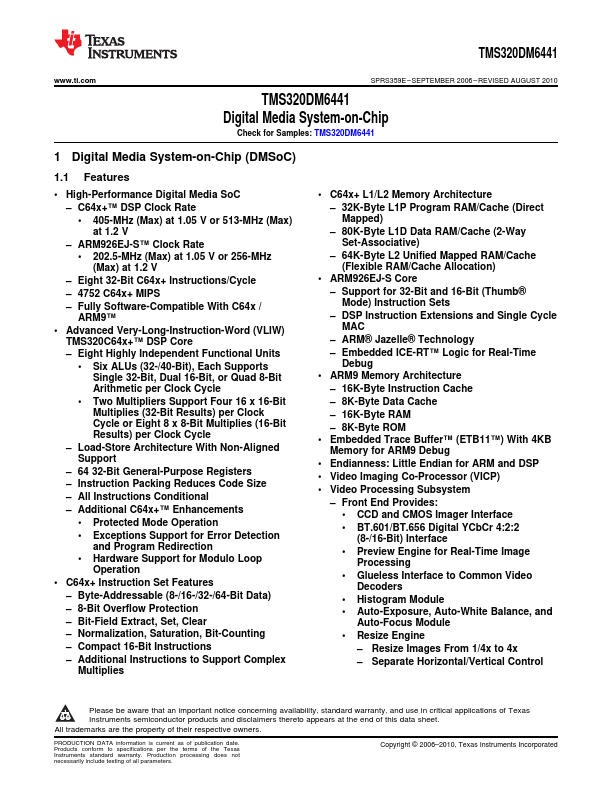

TMS320DM6441

Overview

- High-Performance Digital Media SoC - C64x+™ DSP Clock Rate

- 405-MHz (Max) at 1.05 V or 513-MHz (Max) at 1.2 V - ARM926EJ-S™ Clock Rate

- 202.5-MHz (Max) at 1.05 V or 256-MHz (Max) at 1.2 V - Eight 32-Bit C64x+ Instructions/Cycle - 4752 C64x+ MIPS - Fully Software-Compatible With C64x / ARM9™

- Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x+™ DSP Core - Eight Highly Independent Functional Units

- Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle

- Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle - Load-Store Architecture With Non-Aligned Support - 64 32-Bit General-Purpose Registers - Instruction Packing Reduces Code Size - All Instructions Conditional - Additional C64x+™ Enhancements

- Protected Mode Operation

- Exceptions Support for Error Detection and Program Redirection

- Hardware Support for Modulo Loop Operation

- C64x+ Instruction Set Features - Byte-Addressable (8-/16-/32-/64-Bit Data) - 8-Bit Overflow Protection - Bit-Field Extract, Set, Clear - Normalization, Saturation, Bit-Counting - Compact 16-Bit Instructions - Additional Instructions to Support Complex Multiplies