74AHC273BQ

Overview

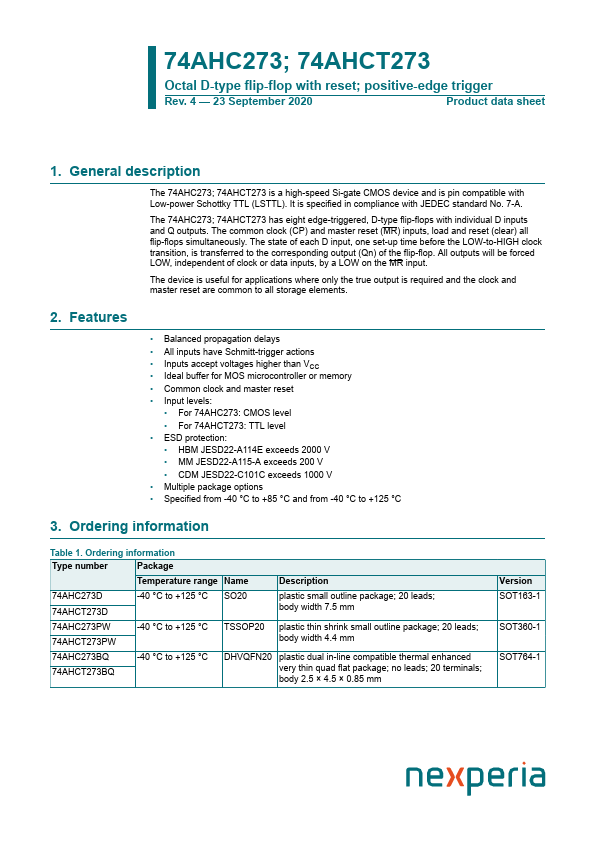

The 74AHC273; 74AHCT273 is a high-speed Si-gate CMOS device and is pin compatible with Low-power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard No. 7-A.

- Balanced propagation delays

- All inputs have Schmitt-trigger actions

- Inputs accept voltages higher than VCC

- Ideal buffer for MOS microcontroller or memory

- Common clock and master reset

- Input levels:

- For 74AHC273: CMOS level

- For 74AHCT273: TTL level

- ESD protection:

- HBM JESD22-A114E exceeds 2000 V