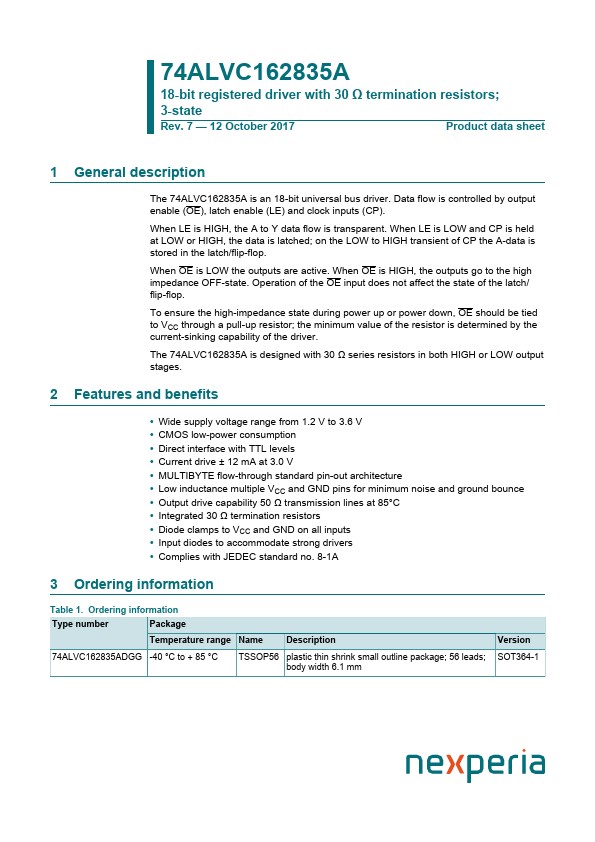

74ALVC162835ADGG Overview

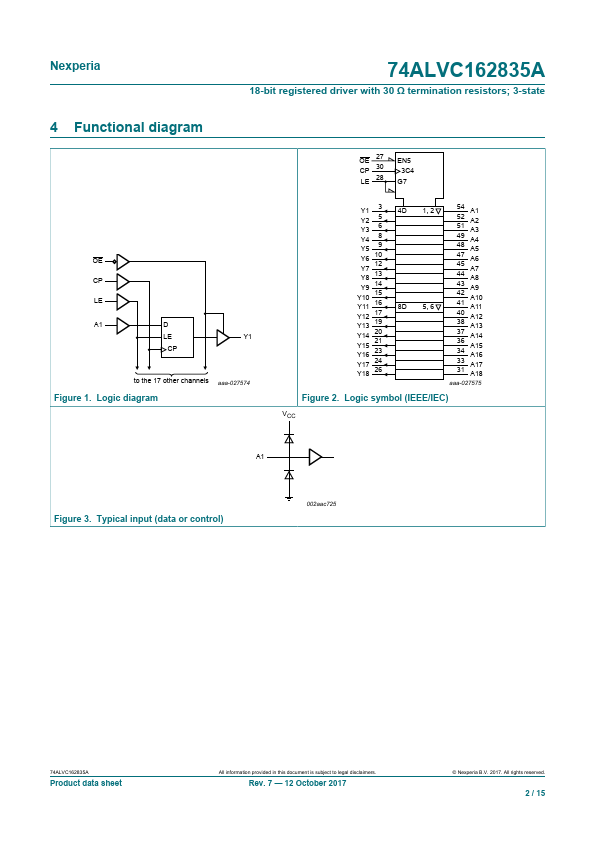

The 74ALVC162835A is an 18-bit universal bus driver. Data flow is controlled by output enable (OE), latch enable (LE) and clock inputs (CP). When LE is HIGH, the A to Y data flow is transparent.

74ALVC162835ADGG Key Features

- Wide supply voltage range from 1.2 V to 3.6 V

- CMOS low-power consumption

- Direct interface with TTL levels

- Current drive ± 12 mA at 3.0 V

- MULTIBYTE flow-through standard pin-out architecture

- Low inductance multiple VCC and GND pins for minimum noise and ground bounce

- Output drive capability 50 Ω transmission lines at 85°C

- Integrated 30 Ω termination resistors

- Diode clamps to VCC and GND on all inputs

- Input diodes to acmodate strong drivers