74AUP1G07 Description

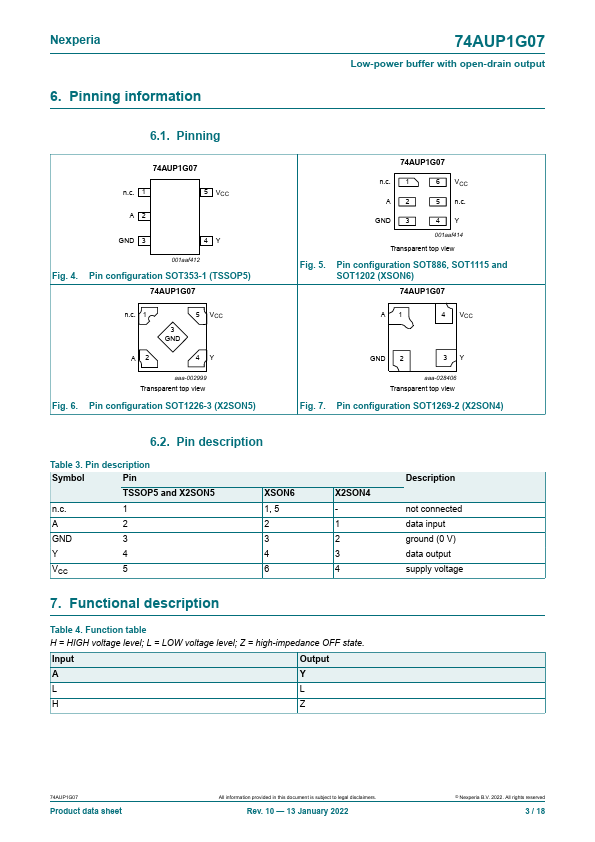

The 74AUP1G07 is a single buffer with open-drain output. Schmitt-trigger action at all inputs makes the circuit tolerant of slower input rise and fall times. This device ensures a very low static and dynamic power consumption across the entire VCC range from 0.8 V to 3.6.

74AUP1G07 Key Features

- Wide supply voltage range from 0.8 V to 3.6 V

- High noise immunity

- CMOS low power dissipation

- plies with JEDEC standards

- JESD8-12 (0.8 V to 1.3 V)

- JESD8-11 (0.9 V to 1.65 V)

- JESD8-7 (1.65 V to 1.95 V)

- JESD8-5 (2.3 V to 2.7 V)

- JESD8C (2.7 V to 3.6 V)

- ESD protection

74AUP1G07 Applications

- Wide supply voltage range from 0.8 V to 3.6 V