74HC73D

74HC73D is Dual JK flip-flop manufactured by Nexperia.

- Part of the 74HC73 comparator family.

- Part of the 74HC73 comparator family.

description

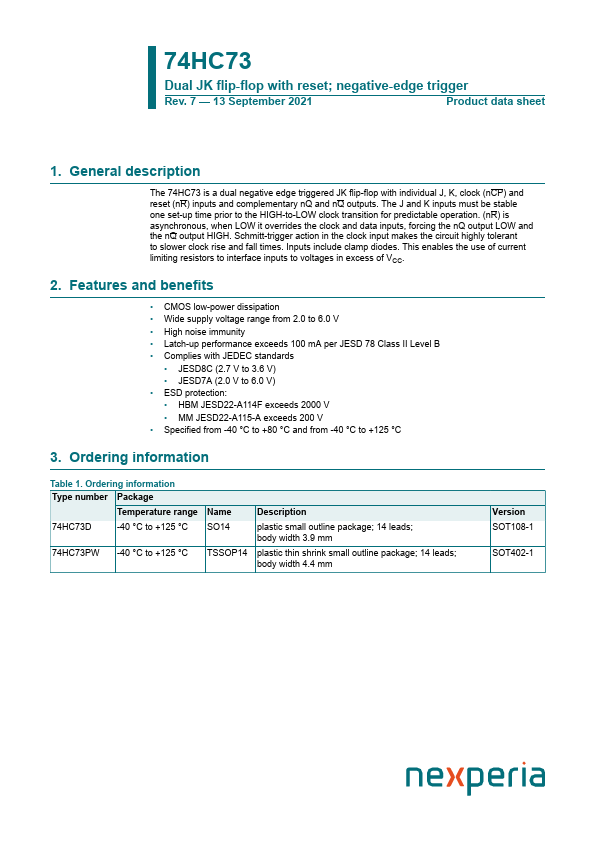

The 74HC73 is a dual negative edge triggered JK flip-flop with individual J, K, clock (n CP) and reset (n R) inputs and plementary n Q and n Q outputs. The J and K inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation. (n R) is asynchronous, when LOW it overrides the clock and data inputs, forcing the n Q output LOW and the n Q output HIGH. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and benefits

- CMOS low-power dissipation

- Wide supply voltage range from 2.0 to 6.0 V

- High noise immunity

- Latch-up performance exceeds 100 m A per JESD 78 Class II Level B

- plies with JEDEC standards

- JESD8C (2.7 V to 3.6 V)

- JESD7A (2.0 V to 6.0 V)

- ESD protection:

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from -40 °C to +80 °C and from -40 °C to +125 °C

3. Ordering information

Table 1. Ordering information Type number Package

Temperature range

-40 °C to +125 °C

74HC73PW -40 °C to +125 °C

Name SO14

TSSOP14

Description plastic small outline package; 14 leads; body width 3.9 mm plastic thin shrink small outline package; 14 leads; body width 4.4 mm

Version SOT108-1

SOT402-1

Nexperia

4. Functional diagram

74HC73

Dual JK flip-flop with reset; negative-edge trigger

14 1J 1 1CP

FF1 CP

1Q 12

3 1K 2 1R

1Q 13

7 2J 5...