Datasheet Summary

74HC165; 74HCT165

8-bit parallel-in/serial out shift register

Rev. 8

- 9 May 2025

Product data sheet

1. General description

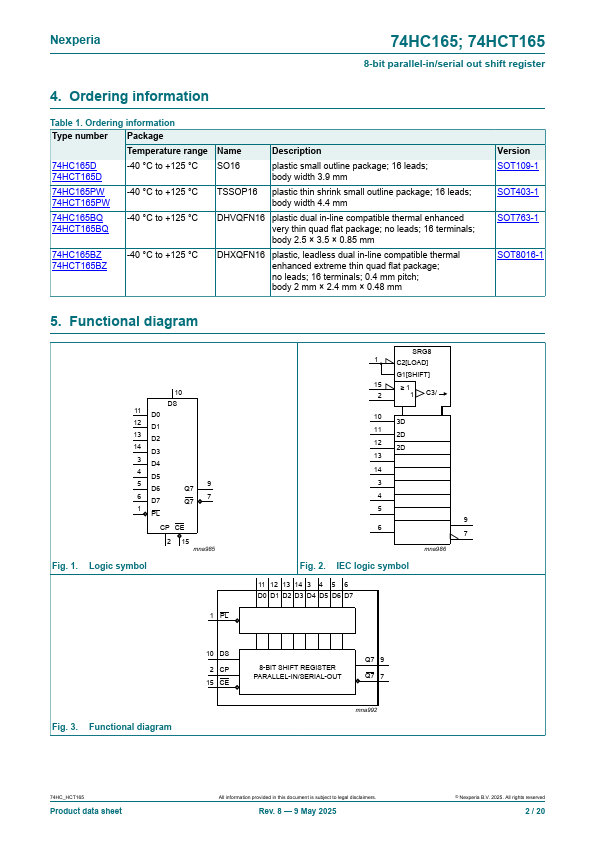

The 74HC165; 74HCT165 are 8-bit serial or parallel-in/serial-out shift registers. The device Features a serial data input (DS), eight parallel data inputs (D0 to D7) and two plementary serial outputs (Q7 and Q7). When the parallel load input (PL) is LOW the data from D0 to D7 is loaded into the shift register asynchronously. When PL is HIGH data enters the register serially at DS. When the clock enable input (CE) is LOW data is shifted on the LOW-to-HIGH transitions of the CP input. A HIGH on CE will disable the CP input. Inputs are overvoltage tolerant to 15 V....