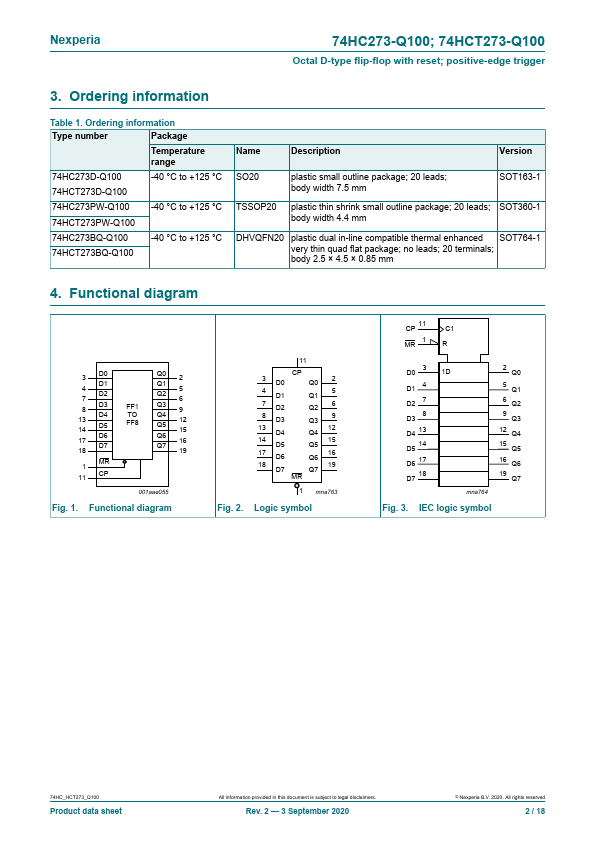

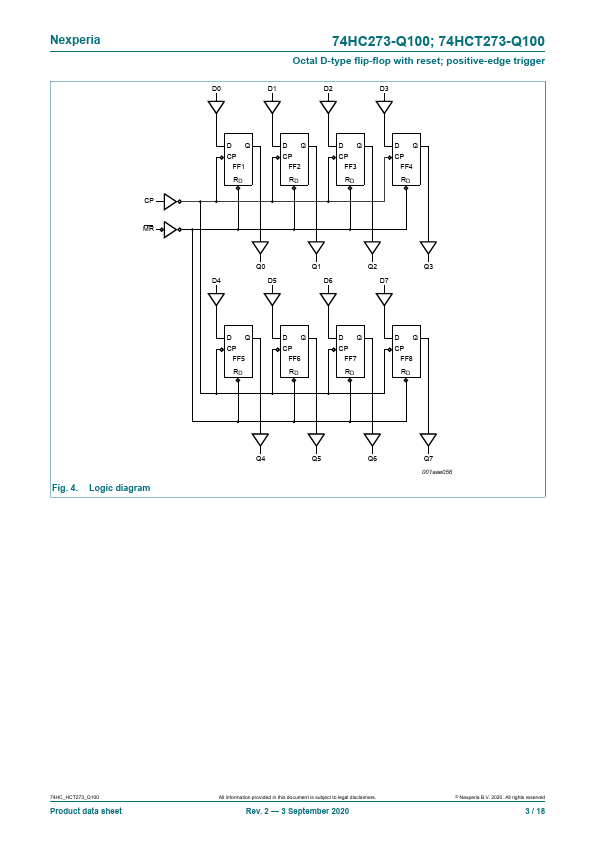

74HCT273-Q100 Description

74HCT273-Q100 is an octal positive-edge triggered D-type flip-flop.

74HCT273-Q100 Applications

- Automotive product qualification in accordance with AEC-Q100 (Grade 1)

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

- Wide supply voltage range from 2.0 V to 6.0 V